# 4-1 結晶成長

(執筆者:鈴木寿一)[2018年7月受領]

半導体デバイス,特に化合物半導体デバイスの作製では、エピタキシャル結晶成長が駆使される.「エピタキシー」「エピタキシャル」とは、成長層の結晶方位が下地の結晶方位と一致していること表す用語である. エピタキシャル結晶成長を実現する代表的な技術である分子線エピタキシー(MBE)や有機金属気相エピタキシー(MOVPE)によって、デバイス層の精緻な作製が可能である.

## 4-1-1 エピタキシャル結晶成長のモード

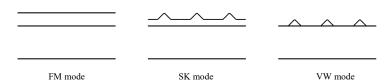

エピタキシャル結晶成長のうち、下地と同じ材料の成長をホモエピタキシャル成長、異なる材料の成長をヘテロエピタキシャル成長と呼ぶ。エピタキシャル結晶成長では、成長する材料と下地となる材料の組み合わせによって、図1・1に示す3つの成長モードが存在する。Frankvan der Merwe(FM)モードは層状の2次元成長モードであり、ホモエピタキシャル成長の場合や、ヘテロエピタキシャル成長であっても、成長結晶と下地結晶の格子定数が一致(格子整合)する場合や、格子定数差(格子不整)が比較的小さい場合に生じる。一方、格子不整が大きいヘテロエピタキシャル成長では、2次元成長の後に島状の3次元成長に移行するStranski-Krastanov(SK)モード、はじめから島状の3次元成長が生じるVolmer-Weber(VW)モードが現れる。

半導体デバイス層の作製においては、FM モードが最も重要である。このモードでの成長層は、格子不整がある場合でも、ある成長膜厚(臨界膜厚)までは、横方向の格子定数を下地と一致させつつ弾性的に歪んでいる。この臨界膜厚を越えるまでの成長をシュードモルフィック(擬似格子整合)成長と呼ぶ。成長膜厚が臨界膜厚を越えると、歪みエネルギーを緩和するために転位の発生を伴う格子緩和が起こり始め、成長層は本来の格子定数に戻っていく。格子緩和の際に発生する転位はデバイス特性に有害であるため、多くの半導体デバイス作製では、格子整合成長あるいは臨界膜厚以下のシュードモルフィック成長が用いられる。一方、大きい格子不整を伴うエピタキシャル成長においては、格子緩和成長が用いられることもある。このときは、比較的厚いバッファ層を成長して充分な格子緩和を起こし、当初の成長モードによらずFMモードに移行させながら、転位密度の低いデバイス層を得ようとする。

## 4-1-2 分子線エピタキシー (MBE) と有機金属気相エピタキシー (MOVPE)

分子線エピタキシー(Molecular Beam Epitaxy: MBE)は、超高真空中の分子線で原料を供給して、基板結晶上でエピタキシャル成長を行う方法である。多くの場合、クヌーセンセル中の原料を超高真空成長チャンバ内で加熱し、チャンバサイズよりも充分長い平均自由行程を有する分子線を供給する。超高真空中における成長であるため、極めて純度の高い結晶の成長が可能である。また、分子線のフラックス制御により、成長速度と組成を制御できる。例えば、AI、Ga、As 原料を加熱して制御された分子線を供給することで、所望の組成の AlGaAs を成長することができる。また、低い成長速度と、各セルの出口に備えたシャッタの高速開閉に基づく分子線供給制御により、原子レベルでの膜厚制御、急峻な異種材料間界面(ヘテロ界面)の形

成が可能である.

MBE 成長では、成長チャンバが超高真空に保たれるため、チャンバ内に質量分析や反射高速電子線回折(Reflection High Energy Electron Diffraction: RHEED)などの分析装置を備えることができ、成長中のその場観察を行うことが可能である。例えば、RHEED における鏡面反射強度の振動から、原子層単位で成長をモニタできる。これらは、成長の精密制御に有効である.一方、装置を超高真空状態を保つ必要があるという点で、MBE は生産技術に適さないとも考えられている.

有機金属気相エピタキシー(Metal-Organic Vapor Phase Epitaxy: MOVPE)は、有機金属と水素化物などを原料として反応管に供給し、基板結晶上の熱分解と化学反応によってエピタキシャル成長を行う方法である。有機金属原料は温度制御されたシリンダに入れられ、 $H_2$ や  $N_2$ をキャリアガスとしてバブリングすることで供給される。原料供給量はマスフローコントローラの流量により制御され、これにより成長速度と組成が制御できる。例えば、トリメチルアルミニウム(TMA)、トリメチルガリウム(TMG)、AsH3を原料として供給することで、所望の組成の AlGaAs を成長することができる。なお、毒性の強い AsH3の代わりにターシャリーブチルアルシン(TBAs)が用いることもできる。

MOVPE によるヘテロ界面は MBE によるものに比べて急峻性に劣ると考えられていた時代もあったが、原料切替え高速化、高流量化、減圧化などによって原料供給の制御性が高まり、MBE によるものと同等なヘテロ界面が得られるようになっている.一方、MOVPE は MBE とは異なり超高真空を必要としないため、装置の大型化が比較的容易である.このため、大面積・多数枚の成長を実現しやすく、生産技術に適していると考えられており、実際に多くの半導体デバイスの生産に利用されている.

図4・1 エピタキシャル結晶成長における3つの成長モード (FMモード, SKモード, VWモード)

# 4-2 ヘテロ接合形成

(執筆者:鈴木寿一) [2018年7月 受領]

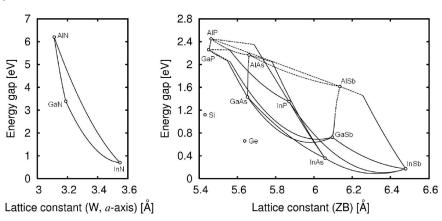

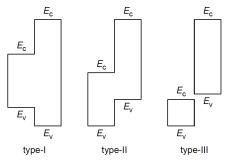

異なる材料間の接合(ヘテロ接合)のエピタキシャル成長による形成は、半導体デバイス作製において極めて重要である。図 2・1 に、室温における化合物半導体材料(混晶を含む)の格子定数とエネルギーギャップの関係を示す。P系、As系、Sb系半導体は閃亜鉛鉱型(Zinc blende:ZB)構造が、また、N系半導体(窒化物半導体)はウルツ鉱型(Wurtzite:W)構造が安定な結晶構造である。これらの材料による様々なヘテロ接合の可能性があるが、多くの半導体デバイス作製では、格子整合成長あるいは臨界膜厚以下のシュードモルフィック成長が用いられており、ヘテロ接合形成においても格子整合あるいはそれに近い材料の組み合わせが用いられることが多い。以下で、ヘテロ接合の具体例について述べる。なお、ヘテロ接合には、伝導帯底( $E_c$ )と価電子帯頂( $E_v$ )のラインアップに応じて、図 2・2 に示すタイプ I(Straddling Gap)、タイプ II(Staggered Gap)、タイプ II(Staggered Gap)、タイプ II(Broken Gap)の可能性がある。多くの例がタイプ I であるが、以下で述べる InAs/AlSb のようにタイプ II のもの、InAs/GaSb のようにタイプ III のものもある。

図2・1 室温における化合物半導体の格子定数とエネルギーギャップ

図2・2 ヘテロ接合のタイプ (タイプⅠ, タイプⅡ, タイプⅢ)

### 4-2-1 GaAs 格子整合系へテロ接合

GaAs/AlGaAs は典型的なタイプ I のヘテロ接合である。GaAs の伝導帯底は AlGaAs の伝導帯底よりエネルギー的に低く、GaAs の価電子帯頂は AlGaAs の価電子帯頂よりエネルギー的に高いため、AlGaAs は GaAs に対して電子・正孔の障壁となる。GaAs と AlAs の格子定数は 殆ど一致しており、Al $_x$ Ga $_1$ - $_x$ As は組成によらず GaAs とほぼ格子整合するため、GaAs/AlGaAs ヘテロ接合は広く利用されている。GaAs/AlGaAs ヘテロ接合は広く利用されている。GaAs/AlGaAs ヘテロ接合において、AlGaAs を  $_x$ 型にドーピングすると、電子がヘテロ界面の GaAs 側に供給され、2 次元電子ガスが形成される(変調ドーピング)。この 2 次元電子ガスは AlGaAs 中のイオン化ドナーと空間的に分離しているため、イオン化不純物散乱が抑制された高い移動度を示し、HEMT (High Electron Mobility Transistor) のチャネルとして利用される。 $_x$ Ga $_x$ As は、 $_x$ Ga $_x$ As は、 $_x$ Ga $_x$ As は、 $_x$ Cipにある。 $_x$ Cipにあ

# 4-2-2 InP 格子整合系へテロ接合

InP には、 $In_{0.53}Ga_{0.47}As$ ,  $In_{0.52}Al_{0.48}As$  などが格子整合するため、これらを組み合わせた InP 格子整合系へテロ接合が利用されている。これらヘテロ接合は InP 基板上エピタキシャル成長による超高速電子デバイスや長波長デバイスにおいて重要な役割を果たす。なお、 $InP/In_{0.52}Al_{0.48}As$  はタイプ II のヘテロ接合である。InP の伝導帯底は  $In_{0.52}Al_{0.48}As$  の伝導帯底よりエネルギー的に低く、InP の価電子帯頂は  $In_{0.52}Al_{0.48}As$  の価電子帯頂よりエネルギー的に低い。このため、 $In_{0.52}Al_{0.48}As$  が InP に対して電子の障壁となると同時に、InP が  $In_{0.52}Al_{0.48}As$  に対して正孔の障壁となる。

## 4-2-3 6.1 Å ファミリーヘテロ接合

6.1 Å程度の格子定数を有する InAs, GaSb, AlSb によるヘテロ接合を 6.1 Åファミリーヘテロ接合と呼ぶ. InAs/AlSb はタイプ II のヘテロ接合であり、InAs の伝導帯底は AlSb の伝導帯底よりエネルギー的に低く、InAs の価電子帯頂は AlSb の価電子帯頂よりエネルギー的に低い、一方、InAs/GaSb はタイプ III のヘテロ接合である。 InAs の伝導帯底が GaSb 価電子帯頂よりもエネルギー的に低いため、GaSb 価電子帯の電子が自然に InAs 伝導帯に移動するという現象が生じる.

### 4-2-4 窒化物半導体へテロ接合

GaN を中心としたウルツ鉱型窒化物半導体へテロ接合は、自発分極とピエゾ分極によって、変調ドーピングを行わなくても 2 次元電子ガスを形成することができるという特徴があり、デバイス応用に有用である.窒化物半導体デバイスは、GaN 基板上成長だけでなく、サファイア 基板、SiC 基板、Si 基板上の格子緩和成長によって作製されている.そのうえで、デバイス層には AlGaN/GaN ヘテロ接合や AlGaN/InGaN ヘテロ接合が用いられる.ただし、格子不整が余り大きくない接合を用いることが望ましい.GaN と格子整合する  $In_{0.17}Al_{0.83}N$  を用いた  $GaN/In_{0.17}Al_{0.83}N$  格子整合へテロ接合のデバイス応用も期待されている.

# 4-5 電 極

(執筆者:大島知之) [2011年12月受領]

電極は、電子デバイスにおいて入出力端子としての機能を担う。三端子デバイスであるトランジスタは、電界効果トランジスタの場合、ゲート、ソース、ドレイン電極によって、バイポーラトランジスタの場合、ベース、エミッタ、コレクタ電極によって、また、二端子デバイスであるダイオードは、アノード、カソード電極によって構成される。これらの電極の形成プロセスは、基本的には金属パターンの形成プロセスそのものにほかならない。したがって、電子ビーム蒸着法に代表される真空蒸着法、スパッタリング法、CVD 法など、ほかの配線形成プロセスと同様のプロセス技術が適用される。

このような電極の中において、電界効果トランジスタのゲート電極の形状は、デバイスの高周波特性に強く影響を与えることから、微細加工を伴う特徴的なプロセス技術が適用される。電界効果トランジスタの電流利得遮断周波数  $(f_T)$  は、近似的には式 $(5\cdot 1)$ で表される。

$$f_T = \frac{g_m}{2\pi C_{ov}} = \frac{V_s}{2\pi L_o} \tag{5.1}$$

ここで、 $C_{gs}$ はゲート容量、 $g_m$ はトランスコンダクタンス, $L_g$ はゲート長、 $\nu_s$ はキャリアの飽和速度を示す。 $f_T$ を高めてデバイスの高周波特性を向上するには,式(5·1)から明らかなように、キャリアの飽和速度が速い材料をチャネルに採用することに加えて、プロセス技術の観点からは、ゲート長の短縮が極めて有効である。

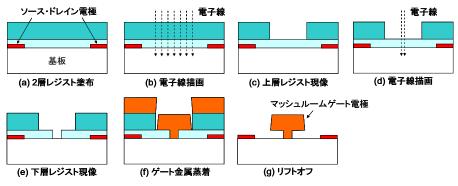

Si CMOS プロセスにおいては、ArF ステッパなどの超微細リソグラフィ技術を核として、既にゲート長は 50 nm 以下の領域にまで短縮化され、近年の CMOS の超高速動作を実現している。一方、ゲート長の短縮は、ゲート金属の断面積が狭くなることによって、ゲート抵抗の増大を招く。GaAs HEMT などの化合物半導体トランジスタが用いられる高周波高出力増幅器 ICでは、 $50\sim200~\mu m$  前後の広いフィンガ長のゲート電極が必要となるため、特にゲート抵抗増大の影響を強く受ける。このため GaAs HEMT においては、マッシュルームゲート、あるいは、T型ゲートと呼ばれる形状のゲート電極が一般的に用いられている。マッシュルームゲートは図  $5\cdot1(g)$ に示したように、断面が T 字の形状をしたゲート電極である。ゲート長は茎部が基板と接する部分の長さで決まるため、ゲート長の短縮を実現しながらも、上部に庇を設けて断面積を広くすることによって、ゲート抵抗の低減を図った構造である  $^{1}$ .

図5・1 に電子線描画法を用いた、マッシュルームゲート形成プロセスの一例を示す. はじめに、基板上に2層の電子線レジストを塗布する. 上層には低分子量の高感度レジストを、下層には高分子量の低感度レジストを選択する. 続いて電子線描画を行って、マッシュルームゲートの庇部のパターンを形成する. このとき、電子線のドーズ量は、上層レジストには感度があって、下層レジストは感度がない程度の、低いドーズ量に設定する. 現像処理を行うと、上層レジストのみに庇部のパターンを形成することができる. 次に、上層レジストに形成した開口部の中に、電子線描画を行ってマッシュルームゲートの茎部のパターンを形成する. 電子線のドーズ量は、下層レジストに対して十分に感度がある高いドーズ量とする. 現像処理を行うと、上層レジストの開口部の中に、下層レジストの開口部が形成される. 続いて、ゲート金属の蒸

着を行う. ゲート金属としては、GaAs HEMT の場合、Au/Pt/Ti や Al/Ti が用いられる. 有機溶剤を用いたリフトオフプロセスにより、レジスト及びレジスト上に蒸着された金属を除去すると、マッシュルームゲートが形成される.

図5・1 マッシュルームゲートの形成プロセス

マッシュルームゲートの庇部と基板との間には、平行平板型の寄生容量を生ずる.  $C_{gs}$ の増加による高周波特性の劣化を抑制するためには、茎部の高さを高くする必要があるが、茎部のみを高くすると機械強度が弱くなる. このため、茎部から庇部にかけて太さを徐々に太くして、断面が  $\mathbf{Y}$  字型になるような工夫がなされることもある.

#### ■参考文献

1) 福田益美, 平地康剛: "GaAs 電界効果トランジスタの基礎,"電子情報通信学会, pp.164-165, 1992.