### ■10 群(集積回路) - 5編(演算・信号処理 LSI)

# 1章 はじめに

(執筆者:吉本雅彦・黒田一朗・天野文雄) [2009年12月受領]

#### ■概要■

本編のはじめに,信号処理/通信処理分野における最近の高性能化の流れ,その VLSI による実現技術(微細化の動向,プロセッサ処理機能の進化,特定用途プロセッサの動向,画像音声符号化機能実現の推移,電力性能の推移),及び実現技術の応用システムへの展開について概観する.

### 【本章の構成】

1-1 節では、各種信号処理技術について高性能化(多機能化)の流れを、車載画像認識および無線通信における処理量のトレンドを例にあげながら概説する。1-2 節では、VLSI による実現技術について、微細化技術の進展により数億から数十億トランジスタ規模の実現が可能になってきていること、汎用プロセッサの処理機能・性能はマルチメディア用演算機能の拡張、マルチコア化、コンフィギュラブルアーキテクチャなどと進化していること、特定用途向け専用プロセッサでは GPGPU、Streem Processer などへの流れがあること、画像音声符号化処理の例ではプロセッサで処理できる範囲が広がってきていること、電力性能の推移では専用 LSI で 100 GIPS/W を超えるレベルが実現可能となってきていること、など最新動向を紹介している。1-3 節では応用システムとしてゲーム、PC、携帯電話への展開を述べる。

# 1-1 高性能化(多機能化)の流れ

(執筆者:吉本雅彦・黒田一朗・天野文雄) [2009年12月受領]

VLSI 技術の発達はより高度な(動) 画像や音声信号の実時間処理や、より高速な有線あるいは無線の通信信号処理の実現を可能にしてきた. 音声,音楽,静止画,動画などの蓄積,伝送のための圧縮,伸長処理,これらの信号から記号情報を抽出する認識処理,これとは逆に記号情報からこれらの信号を生成する合成処理,また変復調あるいは誤り訂正などの通信信号処理などの技術の発展は LSI 技術を最大限に利用することにより、より広帯域・高品質なサービスを普及させてきている。

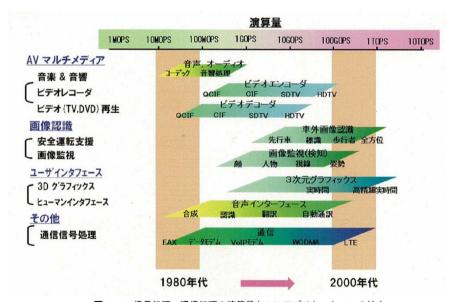

図  $1\cdot 1$  に示すように 1980 年代には毎秒数十から数百 M (1 千万から 1 億) 回の演算能力を実現する LSI によりディジタル音声の圧縮伸長あるいは FAX やモデムの信号処理が実現されていたが,2000 年代には毎秒数百から数千 G (1 千億から 1 兆) 回の演算能力を実現することにより HDTV 信号の圧縮から動画像認識,高速高精細な実時間 3D グラフィックスなどが実現されるようになっている.

図1・1 信号処理・通信処理の演算量と LSI アプリケーションの拡大

なかでも音楽や映像の視聴を可能にする AV マルチメディア分野では、動画の再生(伸長) 処理によりデジタル放送やネットによる映像配信、あるいは CD や DVD などの蓄積メディアによるディジタルコンテンツの普及がもたらされ、一方、動画の圧縮処理により DVD/HDD レコーダやディジタルビデオカメラなどによる動画の記録、蓄積が可能になった。ビデオデコーダ (伸長) LSI、ビデオエンコーダ (圧縮) LSI の性能向上により、携帯電話用の小画面 (OCIF) から HDTV 用の大画面応用まで、画像のサイズ、毎秒フレーム数を増加させると

同時に、より高性能な圧縮方式により高い圧縮率を実現している.

一方, 画像認識の分野では、LSI の高速化、低電力化により、高い認識精度とリアルタイム性を要求される自動車の安全運転を支援する車載の画像認識が実現されてきている。画像認識では、求められる認識精度と認識時間の制約によって所要演算性能が異なるが、例えば顔の検知など時間制約が比較的緩い応用は比較的低い演算性能で実現できるため、携帯電話やディジタルカメラに搭載されるようになってきている。ゲーム機器やユーザインタフェースに用いられる映像合成あるいは3次元グラフィックス処理も動画圧縮、伸張同様、画面サイズやフレーム数に依存するが、これに加えて、生成画像の複雑度や写実性の度合いによっても要求性能が変わってくる。複雑度は、1 秒当たりの描画ポリゴン数や描画画素数(画面サイズとは異なる)により異なり、また、形状やテクスチャ、陰影など写実性を実現する処理の複雑度にも依存する。ヒューマンインタフェースの分野で利用される音声の認識、合成の処理は、認識の正確さ、合成音声の自然さにも依存するが演算性能が数十 MOPS 程度のものから実用化されてきており、より高度な翻訳や自動通訳などの応用も実現されつつある。

通信信号処理としては、数 K から数十 Kbps の有線伝送を実現した FAX やデータモデムなどでは数から数十 MOPS 程度の演算量であったが、近年の数百 Mbps から Gbps クラスのブロードバンド無線伝送を実現する携帯電話システムでは、無線通信処理として数百から数千 GOPS の処理量を必要としている.以下、特に車載画像認識と無線通信分野のトレンドについて紹介する.

### 1-1-1 車載画像認識の例

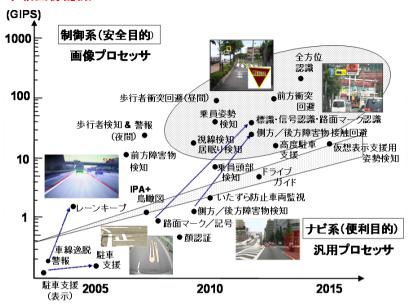

安全運転支援を実現する車載画像認識としては、路上の他の車や障害物や歩行者の認識、信号、標識、その他道路標示(横断歩道などの路面マーク、工事中などの看板)の認識など、車外の環境を認識する処理がある。また車内では、ドライバーの居眠り(まぶたの状況)、顔向き/視線、姿勢の検知、認識などがある。これらのアプリケーション実現に必要な計算量と予想実現時期を図1・2に示す。

特に精度が要求される車の制御系と連携する安全目的の画像認識処理は人の生命に関わる ものであるから、非常に高い信頼性、認識精度が特に要求され、中には数百 GOPS 以上の演 算性能が必要になるものもあり、専用の画像プロセッサが必要になってくる.

一方,カーナビゲーション機能としての車両周囲の物体の鳥瞰図表示や GPS 位置補正に用いる路面マーク認識などの便利目的の画像認識処理は、10 GOPS (1 秒間に 10 <sup>9</sup> 回のオペレーション)程度の演算量に収まると考えられ、マルチコアを含めた汎用プロセッサの進化に合わせて概ね実現可能であると予測されている。

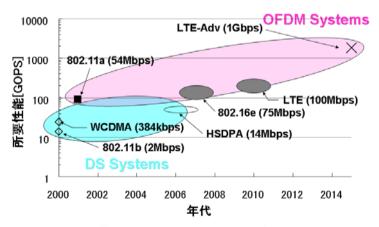

#### 1-1-2 無線通信における処理量のトレンド

無線通信システムではブロードバンド化への流れが急速に進んでおり、携帯電話システムでは 384 kb/s の W-CDMA から 14 Mb/s の HSDPA や 100 Mb/s 以上の LTE, 更には 1 Gb/s の LTE Advanced へと、伝送速度はそれぞれ一桁以上の割合で高速化する.これにともなって変復調方式、誤り訂正方式なども複雑になり、必要な処理量も一桁以上増加する.LTE では 100  $\sim$  200 GOPS 以上,LTE Advanced では 1000 GOPS 以上の演算量が必要になるものと想定される(**図 1・3**).

# 車載画像認識

図1・2 車載画像認識と必要な処理量

図1・3 ワイヤレス通信の所要処理量変遷

システムが複雑になるとともに各種のシステムが混在するようになると、開発費削減などの目的で異なる無線方式を同一のプラットフォームで実現したいという要求も大きくなる. これに対して、プロセッサのファームウェア置き換えで異なる方式を実現するソフトウェア 無線の研究・開発が進められているが、最近では実用的な製品も発表され始めている.

携帯端末についてはまだプロセッサの処理のみですべてのベースバンド機能を実現するのは消費電力的に無理があり、柔軟な構成を有するハードウェアアクセラレータとの組合せを如何に実現するかが現実的な検討のポイントとなっている。将来的には 1 TOPS 程度の処理を 100~200 mW 程度以下で実現可能なプロセッサアーキテクチャの実現が期待される.

# 1-2 VLSI による実現

(執筆者:吉本雅彦・黒田一朗・天野文雄) [2009年12月受領]

#### 1-2-1 微細化技術の進展

### (1) 集積トランジスタ数の推移

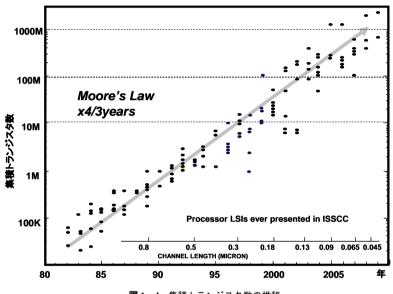

1980 年代初頭に汎用 DSP が出現してからもなお、微細化プロセス技術は進展を重ね、 1 チップ当たりの集積トランジスタ数は、ムーアの法則に従い、3 年で 4 倍の増加率で増大 し続けてきた(図1・4).

**図1・4** 集積トランジスタ数の推移

マイクロプロセッサに搭載されるトランジスタ数は、2000年に5000万個に到達し、最新 鋭のマルチコアプロセッサでは、20億トランジスタを集積したものが出てきている.この集 積素子数の増大により、 演算器の並列化と内蔵メモリの大容量化、 及び専用回路の搭載が可 能となり、信号処理プロセッサをはじめとする SoC の高機能、高性能化をもたらした。

並列アーキテクチャとしては、増大する信号処理演算量をリーズナブルな消費電力で実行 するために、データ演算器の並列化、つまり、時間並列のベクトルパイプライン処理、空間 並列のシストリックアレイ、SIMD アーキテクチャなどが導入された。また、3 オペランドと DMA データを同時に転送できるデータバスの並列化、データ演算と並列に動作するアドレ ス演算器の導入などである、更に、大量の画像データを高速処理するための内蔵データメモ リの大容量化、及びそれらデータを並列バスに同時に供給できる内蔵データメモリのマルチ ポート化なども高速演算に大きく寄与している。また、データ演算回路の専用化設計として は、フィルタリングや行列演算を高速処理するための積和演算器(並列乗算回路とアキュム

レータ) の内蔵に始まり、実時間パターンマッチング処理を実現するための、差分絶対値和 回路や差分自乗和回路の組み込みが、集積素子数の増加とともに実現されていった。

#### (2) クロック周波数の増大

比例縮小則に従った,論理回路の遅延時間短縮やメモリのアクセス時間短縮が,信号処理 LSI の動作クロック周波数を増大させてきた.代表的なマイクロプロセッサのクロック周波数は,この30年の間に3桁近い向上を示している.高速化のためのトランジスタのしきい値電圧の低下がリーク電流を増大させ消費電力特性に悪影響を及ぼし始めたため,昨今では動作周波数の伸びはなくなった.しかし,これまでの動作周波数の増加は,前述の回路の徹底した並列化と相まって,信号処理回路の演算能力(MOPS)を劇的に改善してきた.

#### 1-2-2 汎用プロセッサにおける処理機能、性能の進化

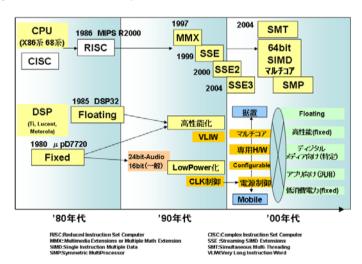

CPU、DSP における信号処理機能強化の流れを**図 1・5** に示す. インテル系 CPU ではマルチメディア処理機能強化のために、1997 年にマルチメディア用演算機能(MMX)を搭載、SIMD 処理の概念が導入された.また、1999 年にはマルチメディア用演算機能を拡張した SSE (Streaming SIMD Extensions) 命令が発表され、機能強化された.その後も 2000 年に SSE 2、2004 年に SSE 3、・・・と機能強化が進められている. 更に、最近では SMT (Simultaneous Multi Threading)、マルチコア化、SMP(Symmetric Multi Processor)などの開発へと進展している.

図1・5 プロセッサ信号処理機能の進化

一方,ディジタル信号処理を実現するのに適した専用プロセッサとしての DSP は,商用ベースでは 1980 年に NEC,及びベル研から発表された 16 ビットの固定小数点型 DSP が最初である。その後,1985 年にベル研より浮動小数点型 DSP の DSP 32 が発表された。固定小数点型 DSP の主流は 16 ビット精度のものであったが、オーディオ信号処理では 20 ビット以上の精度が必要なことから、24 ビット精度の固定小数点型 DSP も各種開発された。1980 年

代後半から 1990 年代初頭は国内では最初のディジタル携帯電話システムが立ち上がる時期であり、標準の音声 CODEC を低消費電力で実現することに的を絞った専用 DSP が各社で開発された. その後もベースバンド処理、画像処理などのマルチメディア処理へと実現機能の範囲を広げながら、低消費電力化の努力が続けられている.

DSP の高性能化については、VLIW アーキを採用した TI 社 TMS 320Cxxx シリーズなどがある。最近では図 1·5 に示したように、据え置き型装置から携帯端末に到る幅広い応用分野に対して、マルチコア化、コンフィギュラブルアーキテクチャ、電源制御との組合せによる低消費電力化などの研究・開発が精力的に進められている。

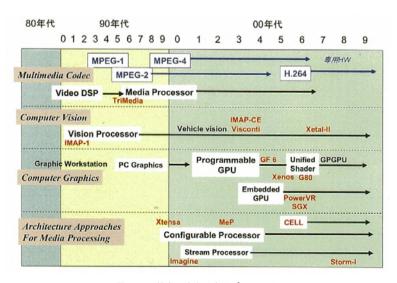

#### 1-2-3 特定用途向け専用プロセッサ

動画コーデックは、1980 年代末よりビデオ用 DSP により実現され始めたが、1990 年代半ばから MPEG コーデック LSI が専用ハードウェアとして実現されるようになり、現在に至っている。一方、1990 年代半ばに PC 用のアクセラレータとして主に MPEG デコーダをターゲットとしたメディアプロセッサが出現したが、現在では組込み用途の DSP の一種として使われている。コンピュータビジョン(画像認識)用のプロセッサ LSI は 1990 年前後から開発されていたが、2000 年以降に車載用途を中心に注目を集めるようになり、更に監視やロボットビジョンなどの用途が期待されている。

3D グラフィックス用 LSI は 1880 年代からワークステーション用に開発されていたが, 1990 年代に PC 用アクセラレータとして開発され, 2000 年以降になって, 複雑化する 3D 処理に対応するためにプログラマブルなプロセッサ(GPU) として高性能化を進めてきた. 現在では汎用な並列プロセッサとして 3D グラフィックス以外の用途にも適用されるようになってきている(GPGPU).

図1・6 特定用途向け専用プロセッサ

一方,携帯電話などの組込み機器用の 3D グラフィックス LSI (IP コア) もプログラマブル GPU 化が進んでいる. その他,主にメディア・信号処理をターゲットとしたプロセッサとして、高性能マルチコアプロセッサ CELL、命令セットなどをユーザがカスタマイズ可能なコンフィギュラブルプロセッサ、動画処理や 3D 処理などのストリーム処理をターゲットとした並列アーキテクチャを採用したストリームプロセッサなどが提案、実用化されている.(図1・6)

### 1-2-4 機能・性能に応じた実現方法の推移(画像音声符号化処理の例)

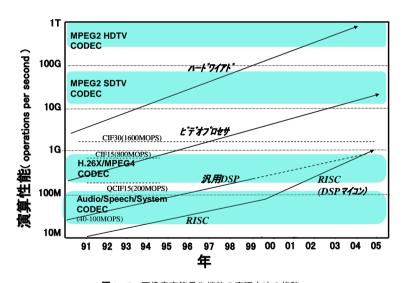

画像音声符号化機能の実現方法の推移を**図 1·7** に示す。ここでは、信号処理 VLSI の実装 方法分類として、RISC/DSP、メディアプロセッサ、ハードワイアドに分類している。また、要求される演算負荷として、音声・オーディオコーデックは数 10 MOPS~100 MOPS、携帯機器応用の H.26X/MPEG-4 コーデックは数 100 MOPS~1 GOPS 程度、標準 TV 画像対応の MPEG-2 コーデックは数 10 GOPS、HDTV 画像対応の H.264 コーデックでは数 100 GOPS~1 TOPS が必要とされる。

図1・7 画像音声符号化機能の実現方法の推移

これに対して、各実装方法の演算性能は微細化とともに年々増大してきた.携帯機器応用の H.26X/MPEG-4 コーデックは、21 世紀初頭には RISC 上での実装が可能となり、つまりソフトウェア実装が低消費電力で実現できていることを示している.一方、HDTV 画像対応のH.264 コーデックを実用化可能な消費電力で実現するには、依然、ハードワイアド実装が必要である.図1.7 に見られる動向は、音声画像符号化処理のソフトウェア実装の領域が徐々に広がってきていることを示している.

信号処理 LSI の高性能化,高機能化の重要な技術動向として,プロセッサ回路とハードワ

イアド回路のハイブリッドアーキテクチャがある. 信号処理の階層構造の例として画像符号 化処理の階層構造を示す ( $\mathbf{表 1 \cdot 1}$ ).

| _      | 符号化の階層化        |                                                         | 14 AM TENE                          | 高速性                 | 並列性 | ————<br>柔軟性 |

|--------|----------------|---------------------------------------------------------|-------------------------------------|---------------------|-----|-------------|

| 動画像符号化 | 単位             | 内容                                                      | 演算種類                                | 同丞江                 |     |             |

|        | フレ<br>ーム<br>以上 | <ul><li>・システム制御</li><li>・符号化制御</li><li>・ビデオ多重</li></ul> | 逐次処理                                | 数十MHz<br>▲          | 困難  | *           |

|        | ブロック           | ・可変長符号<br>化/復号化<br>・ブロック属性判定<br>・MCベクトル判定               | ビッ ト操作<br>条件分岐<br>ルックアップ<br>テーブル等   |                     |     |             |

|        | 画素             | ・量子化∕逆量子化<br>・動き補償<br>・DCT//DCT<br>・画像フォーマット<br>変換      | ルックアップ<br>テーブル<br>Σ ax<br>Σ  x-y など | ▼<br>数百MHZ~<br>数GHz | ▼容易 | <b>小</b>    |

表1・1 信号処理の階層構造における処理内容分析(画像符号化の例)

処理単位として、画素レベル、ブロックレベル、フレーム以上として分類する。画素レベル処理には、画像フォーマット変換、DCT/逆 DCT、量子化/逆量子化、動きベクトル検出処理などがあり、実行される演算としては、積和演算、差分絶対値演算などがある。ブロックレベルとしては、MC ベクトル判定、ブロック属性判定、可変長符復号化処理などがあり、ビットマニピュレーション、ルックアップテーブルなどがある。フレーム以上では、ビデオ多重やレートコントロールなどの逐次処理が主流となる。表 1·1 から明らかなように、画素レベルほど高速性能が要求されるが定型処理となることが多い。一方、フレーム以上の処理になるほど、高速性能は要求されないが、処理の柔軟性が要求される。また、並列実装は画素レベルほど容易である。

以上の画像符号化信号処理の階層構造を考慮することで、プロセッサ回路とハードワイア ド回路のハイブリッドアーキテクチャが多くの開発において採用されている。フレーム以上 の処理はプロセッサ上のソフトウェアで実装し、高画質、高精度な処理を実現するとともに、 画素レベルになるほど並列化された専用エンジンを導入することで、低消費電力で実時間処 理を実現する.

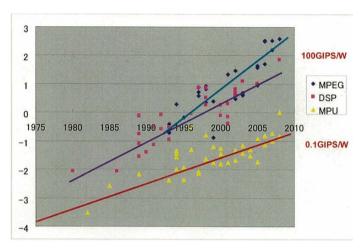

#### 1-2-5 電力性能の推移

図1・8 はメディア処理性能を中心に専用 LSI, DSP, MPU の電力性能の推移を示したものである. 専用 LSI (MPEG コーデック) の電力性能は 10 年で約 2 桁向上し, 2000 年代半ばに 100 GIPS/W を超えるレベルになっている. 同じく DSP やメディアプロセッサの電力性能は 15 年で約 2 桁向上するというペースで 10 GIPS/W の電力性能を実現している.

一方, MPU(主にハイエンド系)は、並列化のために制御系にハードウェアリソース、電力リソースを投入し続けているため、10年で約1桁向上するというペースであり、0.1 GIPS/W

程度になっている。 ただし、 最先端プロセスを利用した MPU では 1 GIPS/W を達成するものも出てきている.

図1・8 GIPS/W の推移 (ISSCC で発表された MPEG, DSP, MPU)

# 1-3 応用システムへの展開

(執筆者:吉本雅彦・黒田一朗・天野文雄) [2009年12月受領]

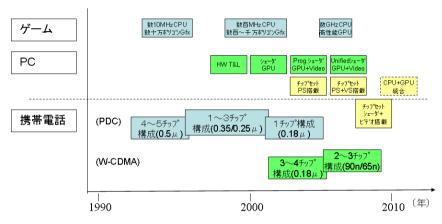

応用システムにおける SoC 化の流れを**図 1・9** に示す. ゲーム機器では約 5 年ごとに CPU 及びグラフィックス, サウンド処理 LSI を  $1\sim2$  桁性能強化した新しい機種が導入されているが, 新チップ導入時においては, これまでのところそれぞれのチップは別チップという構成は変わっていない.

図1•9 各システムにおける SoC 化の流れ

PC 用の(単体の) GPU は頂点処理 (1999年), 画素処理 (2001年) とハードウェア化が進み 2004年には、各々の処理がプログラマブルなシェーダとして実現され、更に (MPEG) ビデオハードウェアが搭載された。更に、2005年から 2006年にかけて頂点、画素の各シェーダが統合され、高性能な並列プロセッサとしてのグラフィックス以外の応用にも利用されるようになってきた。

一方、PC 用チップセットにおいても、頂点処理シェーダが搭載され (2004 年), 2006 年に は画素処理も含め統合シェーダとして搭載されるようになってきている。 更に 2008 年には HD ビデオや、ブルーレイ再生機能も搭載されている。 今後はチップセットの GPU を含めた機能 (ノースブリッジ) と CPU の統合も予定されている。

携帯電話のベースバンド処理+アプリケーション処理部は、PDC システム初期の頃には変調、復調、TDMA 制御、CPU、DSP など 10 チップ程度の LSI で構成されていたが、その後各機能の統合化が進み 2000 年前後には 1 チップ LSI が実現された。W-CDMA システムではPDC システム以上に複雑な処理が必要であるが、プロセス技術の進歩などもあって初期には $3\sim4$  チップで構成され、最近では  $1\sim3$  チップ程度で実現されている。

以上、概要を述べた、第2章以降で各項目について詳述する、