# ■10 群 (集積回路) - 5 編 (演算・信号処理 LSI)

# 4章 各種システム・分野への応用

(執筆者: 天野文雄) [2010年3月 受領]

## ■概要■

本章では、信号処理/通信処理の各種システム/分野への応用例について紹介している。 通信分野ではネットワークプロセッサ、省電力無線システムの例を、家電系ではディジタル TV、ゲーム機の例を、制御系ではロボット、および車載系の例を説明している。

### 【本章の構成】

- 4-1 節では、通信制御、プロトコル処理のためのネットワークプロセッサについて、ソフトウェアの改善、周波数の高速化、プロセッサのマルチコア化、ネットワーク処理のハードウェア化の流れを解説している。また、ハードウェア化の具体例として TCP/IP 処理のスループットが一桁改善する例を紹介している。

- 4-2 省電力無線システムでは、Bluetooth および ZigBee の変復調で必要となるディジタル信号処理技術を紹介している.

- 4-3 節では、家電系の例としてディジタル TV 用 SoC の基本構成, TS 処理と AV 同期機構, ビデオおよびオーディオデコード, ビデオ表示制御, 外部メモリ制御について説明している. DVD についても概要を説明している.

- 4-4 節は、ゲーム機に関する節である. 家庭用ゲーム機の変遷、ゲーム機の構成、今後の動向を述べている. また、ゲーム向け CPU の具体例として、Cell Broadband Engine プロセッサの基本構成と特徴を説明している.

- 4-5 ロボットでは、まずネットワーク関連としてセンサネットワーク、リアルタイムネットワークの概要、及びロボット向けネットワーク規格の概要を解説している。また、いくつかのコントローラの例と分散リアルタイムシステムを実現するための RMT Processor、いくつかの画像処理 LSI、及びビジョンチップを紹介している。

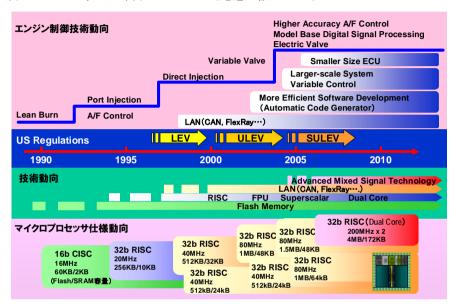

- 最後に 4-6 車載 LSI では、車載情報系、ボディ系、セーフティ系、パワートレイン、シャーシ系、X-by-wire 系の各応用分野があることを述べた後、燃費関連の技術動向、エンジン制御技術およびマイクロプロセッサ仕様/性能の動向、車載情報系マイクロプロセッサ要求性能の動向を述べ、最後に第1世代~第3世代のハイエンドナビ用プロセッサの例を紹介している。

# 4-1 無線システム

(執筆者:中瀬博之) [2010年1月 受領]

通信におけるディジタル信号処理は、特に通信制御(MAC)、TCP/IP のプロトコル処理は 組込み CPU により処理されている。組込み CPU は、特にモバイル端末において ARM 社製 プロセッサの独壇場であり、世界シェアの 80 %以上を占めている。日本国内においても、日立の SH、NEC の V シリーズと三分しており、今後ますますそのシェアを伸ばしていくこと が予想されている。

本節では、日本のベンチャー企業によって開発された通信用 LSI (ARTESSO, ネットクリアスシステムズ) のアーキテクチャと動作について紹介する.

# 4-1-1 ネットワークプロセッサ

ノートPC,携帯電話,ディジタルTV,DVD/ブルーレイプレーヤ,ゲーム機,家電製品に至るまで現在市販されているエレクトロニクス機器は、ほとんどすべてがネットワークへの接続機能を有している。もちろん、インターネットへの接続を実現するためネットワークの事実上の成果標準となっているTCP/IPがプロトコルとして装備されている。

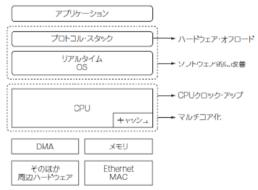

図4・1 一般的なネットワークプロセッサの構成

図4・1は、ネットワーク接続機能としてイーサネットを装備し、一般的なプロセッサを用いた場合の通信機能のシステム構成を示している。エレクトロニクス機器の CPU には、リアルタイム OS(RTOS)が実装され、RTOS 上に TCP/IP を実現するプロトコル群がソフトウェアとして装備される。 CPU は同時にイーサネットコントローラのハードウェア制御を行い、通信機能を実現する。この構成において、通信機能の性能向上(高速化、低消費電力化)を実現するための手法として、主に以下に示す 4 通りが考えられる。

### (1) ソフトウェアの改善

通常、ネットワーク処理はRTOS上で実行されるプロトコルスタックで構成されている。これらのソフトウェアを改善にすることは重要であるが、既に様々な手法が用いられており、今後の大幅な性能改善の余地は少ないといえる。

# (2) プロセッサ周波数の高速化

従来の構成のまま CPU の動作速度を高くすることで、通信速度の高速化を実現することが可能である。周辺の LSI の動作速度を同時に引き上げる必要があるものの、既存の開発資産(ソフトウェアなど)に全く影響を与えず、単純に高性能を得る手法として有効である。しかし、高速化に比例して消費電力が増加すること、高い周波数で動作する CPU の開発が必要なこと、コスト高な先端プロセスによる製造によりチップコストが上昇すること、などのデメリットがある。

## (3) プロセッサのマルチコア化

マルチコア技術は現在の PC 用プロセッサの高性能化の主流であり、組込みシステムでも採用され始めている。処理性能の向上をクロックアップと同時に用いることで高性能化が可能であると同時に、クロックアップのみの場合と比較して消費電力の抑制が可能であるといわれている。しかし、ハードウェアのもつ性能を十分に引き出すためには、巧みなマルチスレッドプログラミングが必要であり、従来の開発資産や開発環境・手法をそのまま利用できない場合が多い。また、物理的なチップサイズが大きくなることからチップコストも高くなる。

### (4) ネットワーク処理のハードウェア化

従来ソフトウェアで処理していたネットワーク処理の全体もしくは一部機能を、ハードウェア化手法でオフロード(「荷物を降ろす」の意味、ソフトウェアの処理負担を減らすこと)と呼ぶ、チェックサム処理、TCPセグメント処理などハードウェアの得意な機能の部分的なオフロードから、TCP/IP全体をオフロードする TOC (TCP/IP Off Load) まで様々な技術がある。高速化・低消費電力化を同時に実現することが可能であるが、柔軟性を失うため用途を特定した場合にのみ有効である。

以上のように、従来の技術の延長線上での性能向上手法では、ソフトウェアの柔軟性を確保しつつ、安価で高速化、低消費電力化を獲得することは容易でないことがわかる.

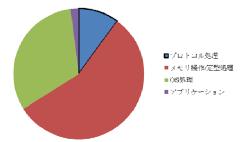

次に、現在のネットワーク処理の実態を把握し、ネットワーク処理において最も負荷が大きく改善効果が期待できる機能を明確化する. 一般的なプロセッサに RTOS を実装し、商用の TPC/IP プロトコルスタックで、連続的に 1460 バイトの TCP/IP パケット受信を実行したときの分析から処理時間の割合を明確化する. 受信したパケットは廃棄し、受信後の処理は存在しない状態とした. プロセッサのクロックは 50 MHz、パケットの転送速度は約 12 Mbps とクロック速度の約 24 %である.

**図4** • 2 従来のソフトウェア処理による TCP/IP 処理の内訳

図4・2 に、従来技術による TPC/IP 処理サイクルの内訳の例を示す. プロトコル処理は 10 %, アプリケーションが 2 % と、すべてを合計してもプロセッサの処理時間の 10 %程度であることが明らかになった. その反面, OS 自体の処理時間は 32 %, メモリコピー, ヘッダ解析などの処理は単純であるが時間のかかる処理が 56 %, 合わせて 88 %の時間を消費していることがわかる.

TPC/IP の機能をすべてハードウェア化すると処理時間を劇的に短縮することが期待できるが、ハードウェアに起因する通信ポート数の制限や、プロトコルの仕様変更や拡張に対応できないなどの問題が発生する.しかし、処理内容の分析により、TCP/IP プロトコル処理をソフトウェア制御で柔軟性を残しても、メモリコピーなどの定型処理、RTOS のハードウェア化で通信速度の高速化を実現できる可能性があることが明らかになった.

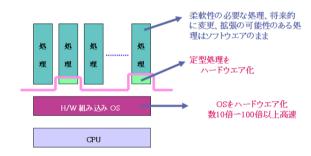

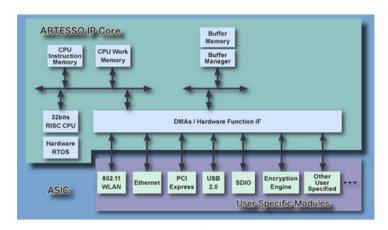

# 4-1-2 ARTESSO プロセッサの構成

**図 4・3** にネットクリアスシステムズ社製 ARTESSO プロセッサのコンセプトを、**図 4・4** に構成を示す。32 bit RISC プロセッサに、(1)ハードウェア化した RTOS、(2)ハードウェアバッファ管理、(3) DMA 機能、(4)ハードウェア関数、から構成される。

図4・3 ARTESSO プロセッサのコンセプト

図4・4 ARTESSO プロセッサの構成

### (1) ハードウェア RTOS

TCP/IP 処理サイクルのうち、RTOS に費やされる時間は約3割になることが分析から明らかであり、RTOS 処理をハードウェア化すると高速化への改善効果は大きい。ARTESSOでは、μITRON 4.0 のサブセットをハードウェア化した。セマフォイベントメールボックスなどの同期/通信用システムコール、タスクの起動・終了などのタスク管理システムコール、ディスパッチ制御や CPU ロック制御などのシステム状態管理システムコールなど、30以上のシステムコールを実装している。従来の ITORN のソフトウェア資産を容易に導入することができる。また、割込み発生から ISR 起動までは9クロック、更に「ISR をハードウェア化したモード」で動作させると、割込み発生からディスパッチ完了まで 20 クロック前後という

整異的なリアルタイム性を実現している。

表 4・1 に、RTOS の性能比較として、CPU クロックサイクル数についてハードウェア OS と RTOS についてまとめた。すべてがソフトウェアにより実装された RTOS と比較して、数十倍から数百倍の速度で動作している。ハードウェア RTOS のシステムコール呼び出しは、通常の関数呼び出しと同様に、決められた呼び出し規則に従ってレジスタに値をセットし、特定のアドレスに対して CALL 命令を発行することにより実行する。プログラミングの観点からみると、呼び出したシステムコールがハード、ソフトのどちらで構成されているか区別できない。したがって、プログラミングモデルに特別な変更を必要としない。

**表 4・1** RTOS の性能比較 (機能を呼び出した際に必要とするクロックサイクル数. ディスパッチをともなう動作の場合はその時間も含む)

| 機能           | ARTESSO | RTOS A | RTOS B |

|--------------|---------|--------|--------|

| 起床待ち         | 11      | 628    | 1367   |

| タスクの起床       | 11      | 496    | 1014   |

| メールボックスからの受信 | 14      | 591    | 1173   |

| メールボックスへの送信  | 13      | 541    | 1673   |

| イベントフラグ待ち    | 12      | 611    | 3316   |

| イベントフラグセット   | 12      | 660    | 1103   |

| セマフォ待ち       | 12      | 558    | 3181   |

| セマフォ退却       | 14      | 536    | 1618   |

### (2) ハードウェアバッファ管理

バッファメモリは、イーサネット、TCP/IP などの送受信フレームを一時的に退避する目的で使用し、パケットの送受信の際に必ず利用する.プロトコル処理において、送受信データ用バッファの用途で頻繁にメモリ確保、解放の操作が頻繁に行われるため、ソフトウェアにとっての負担になる.ハードウェア化により、メモリ管理自体の高速化とともにバッファの自動確保、解放の機能を実装することでソフトウェアの負担を低減する.バッファメモリは、バッファマネージャに管理されており、メモリを必要とするタスクに対してメモリの割当て、解放などを迅速に行うことによりバッファメモリを効率的に運用する.

#### (3) DMA 機能

DMA 機能をハードウェア化し、メモリコピー処理を低減する. ハードウェア関数とし

て DMA を実装することで、プロトコル処理の 56%に及ぶメモリ操作処理を低減することで、高速化と低消費電力化を実現している. DMA 機能は、プロセッサの外側に様々な機能を容易に接続するための共通のインタフェースとして実現している. イーサネットや無線 LAN などのネットワークインタフェースや PCI Express、SDIO、USB などのバスインタフェース/周辺インタフェースを接続実装できる.

## (4) ハードウェア関数

暗号・復号回路などの定型処理でハードウェア回路の方が高速な処理となる機能を「Hardware Function」として登録し、Hardware Function IF に接続して利用する。ハードウェア関数は、プロトコルヘッダの各フィールドを構造体のメンバに代入する単純処理、DMA などの周辺ハードウェアを制御するためのロジックをハードウェア化し関数として呼び出せるように実装している。ライブラリ関数を呼び出すようにハードウェアの機能を利用できる。RTOS と同様に、プログラミングからは、通常の関数と同様に記述できるため、特別な変更が必要ない。

メモリ操作、プロトコルヘッダ解析などの定型処理のみを注意深く選択しハードウェア化することで、柔軟性の喪失を最低限に抑えながら大幅な性能向上を実現している。ハードウェア化した機能は関数呼び出しの形で実現しているため、プログラミングやコンパイラに対して特別な機能や配慮を行う必要がない。また、ハードウェア化した機能以外は従来どおりソフトウェアで実現するため、ハードウェア化による高速化の実現とともにソフトウェアによる柔軟性を両立している。

## 4-1-3 TCP/IP の性能比較

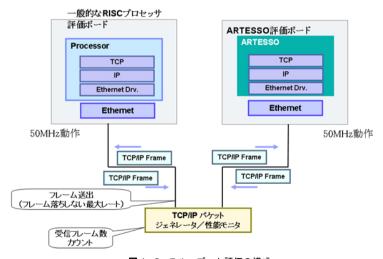

ARTESSO を用いた場合の TCP/IP パケットの転送速度を, ARM 9 にソフトウェアで実装した場合と比較して性能評価を行う. ARTESSO 及び ARM 9 は評価ボートとして構成し、ギガビットイーサネットによりパケットジェネレータ/モニタと接続する (図 4・5).

図4・5 スループット評価の構成

ARM 9 には、商用のソフトウェア RTOS とプロトコルスタックを実装した. 双方の動作クロック周波数は50 MHz とした. 1460 バイトの TCP/IP パケットを連続的に送信し、受信パケットは直ちに破棄することで CPU の能力をすべてパケット送受信に利用できるようにした.

表 4・2 に計測結果を示す. ARTESSO はハードウェア化の効果により, 従来のソフトウェア制御の TCP/IP 処理の 10 倍以上のパケット送受信能力を有していることがわかる.

| 2 101/11 1/11     |                  |               |  |

|-------------------|------------------|---------------|--|

|                   | ARM 920T         | ARTESSO       |  |

|                   | 動作クロック 50 MHz    | 動作クロック 50 MHz |  |

| I-Cache: 16 k バイト |                  | Cache; なし     |  |

|                   | D-Cache:16 k バイト |               |  |

| TCP 送信            | 12 Mbps          | 132 Mbps      |  |

| TCP 受信            | 12 Mbps          | 143 Mbps      |  |

**表 4 • 2** TCP/IP スループットの比較

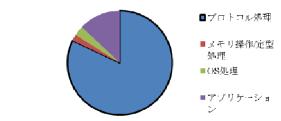

図4・6に ARTESSO における TCP/IP 処理の内訳を示す. RTOS 処理,メモリ操作/定型処理をハードウェア化により高速化することで,プロセッサの処理のうち 95 %の時間を TCP/IP 処理とアプリケーション処理とで利用している. アプリケーション及びプロトコル処理の絶対量は変化していないことから,ソフトウェアによる RTOS 処理から 80 %以上の時間削減を実現したといえる.

図4・6 ARTESSO による TCP/IP 処理の内訳

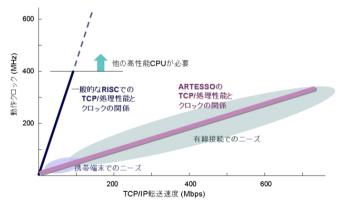

**図 4・7** TCP/IP 転送速度と動作クロック

図4.7 に ARTESSO を用いた場合のクロック周波数と TCP/IP スループットの関係を示す. 従来の CPU とソフトウェア処理を用いた場合, クロック周波数を 600 MHz で動作させても スループット 200 Mbps を超えることは困難である. 一方, ARTESSO では, 動作クロック 150 MHz 程度でスループット 500 Mbps 以上を実現することが可能である.

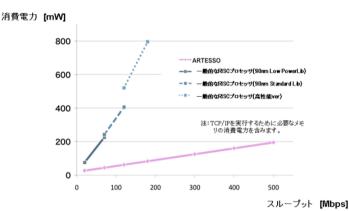

図4・8 に、TCP/IP スループットと処理の際に必要な消費電力の関係を示す。従来の構成では、スループット100 Mbps 以上を実現するためには数百 mW が必要であり、500 Mbps 以上のスループットを獲得するためにクロック周波数を600 MHz 以上で動作させるとその消費電力は数 W に及び、コンシューマ機器への実用的ではない。一方、ARTESSOでは500 Mbpsを実現するために200 mW の消費電力であり、従来の1/10 以下の消費電力を実現している。

図4・8 スループットと消費電力

通信用プロセッサ,特にモバイル端末に用いる CPU はこれまで海外製品に大きなシェアを 奪われていた. 今回紹介した ARTESSO プロセッサのように、用途を明確化し高速化のため の機能分析を行うことにより、通信用ディジタル信号処理デバイスとして高速低消費電力動作を両立するアーキテクチャを実現できることが明らかになった. 今後の日本発のディジタル信号処理技術、LSI の発展に期待したい.

# 4-2 小電力無線システム

(執筆者: 石黒仁揮) [2009年1月受領]

近距離無線通信規格として Bluetooth  $^{1)}$ , ZigBee  $^{2)}$ , UWB などが実用化されている. 特に, Bluetooth, ZigBee は携帯端末, ワイヤレスヘッドセット, マウスなどへの利用, 更にはセンサネットワークへの応用をねらって, 低電力動作のトランシーバが実現できるような変調方式が採用されている. 本節では, 小電力用途の無線規格として, Bluetooth, ZigBee を取り上げ, その変復調器で採用されている信号処理技術について概説する.

# 4-2-1 信号処理技術の動向

一般的に無線通信用トランシーバは、受信系においてはアンテナで受けた信号の増幅、周波数変換、妨害波除去フィルタ、復調器(検波器)で構成される.また、送信系は、変調器、 高周波への周波数変換、電力増幅器から構成される.

Bluetooth, ZigBee はいずれも、低コスト、低電力化のために比較的シンプルな変調方式を採用しており、特に Bluetooth の初期のトランシーバ LSI では簡単なアナログ回路による変復調が採用されていた。しかしながら、プロセス技術の進展とともに、ディジタル回路の面積、及び消費電力が小さくなり、比較的単純な変調方式をもつ Bluetooth、ZigBee においても、素子特性のばらつきに強いディジタル信号処理を用いた変復調が主流となってきた。

以下に、Bluetooth 及び ZigBee で採用されている変調方式、及び代表的な変復調器の構成 について説明する。

# 4-2-2 変調方式

Bluetooth 及び ZigBee の変調方式を、それぞれ表 4·3 及び表 4·4 に示す.

Bluetooth の初期規格 (Basic Rate) においては、周波数変調の一種である Gaussian Frequency Shift Keying (GFSK) が用いられた. 定包絡線変調のため、送信機は VCO の制御端子に Gaussian 波形整形を行ったベースバンド信号を入れる直接変調と非線形高効率電力増幅器を用いることができ、また受信側は従来の Limiter・Discriminator 検波器を用いることができるため、低コストでトランシーバが実装できる。 しかしながら、アナログ方式では VCO 直接変調における周波数ドリフト、受信側アナログチャネル選択フィルタの特性ばらつきなどの問題があり、次第にディジタル変調方式に置き換わってきた。 更に、データレートの改善をねらって策定された Enhanced Data Rate (EDR) 規格では、 $\pi/4$ -QDPSK (2 Mbps)、8 DPSK が変調方式として採用され、ディジタル信号処理を用いた変復調器が必須となった。

| Z. Diactori vyzilivy |                 |           |                         |        |

|----------------------|-----------------|-----------|-------------------------|--------|

|                      | Basic rate      |           | Enhanced Data Rate (EDF |        |

| 利用周波数帯               | 2.4 GHz IMS バンド |           |                         |        |

| 変調方式                 | GFSK            | π/4-DQPSK |                         | 8 DPSK |

| スペクトラム拡散方式           | 周波数ホッピング        |           |                         |        |

| データレート               | 1 Mbps          | 2 Mbps    |                         | 3 Mbps |

表 4・3 Bluetooth の通信方式

ZigBee は、センサネットワーク的な用途(ビル、工場管理のオートメーション化など)を 狙って、Bluetooth よりも更に低電力、低コスト動作を目指して規格が策定された。変調方式 として、BPSK、Offset-QPSK(OQPSK)が、スペクトラム拡散方式として周波数ホッピング よりも実装しやすい直接拡散が採用された。

| <b>数・・・</b> Zigbte の過日万式 |                 |         |          |

|--------------------------|-----------------|---------|----------|

| 利用周波数帯                   | 868 MHz         | 915 MHz | 2.4 GHz  |

| 変調方式                     | BPSK            | BPSK    | OQPSK    |

| スペクトラム拡散方式               | 直接拡散            |         |          |

| データレート                   | 20 kbps 40 kbps |         | 250 kbps |

表 4 · 4 ZigBee の通信方式

## 4-2-3 復調器におけるディジタル信号処理

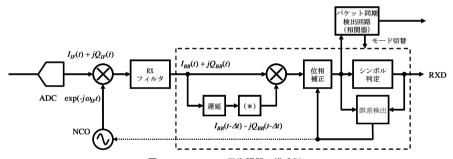

Bluetooth, ZigBee の受信機アーキテクチャとしては、ワンチップ化に向いた Low-IF 方式 もしくはダイレクトコンバージョン方式が採用されることが多い. **図 4·9** に一般的な復調器 の構成を示す. ある程度のチャネル選択(近接妨害波除去)をアナログ領域で行い, AD 変換後に完全な妨害波除去やディジタル復調などを行う.

図4・9 Bluetooth 用復調器の構成例

Low-IF 方式においては、NCO を用いて IF 信号からベースバンド信号に周波数変換を行い、ディジタルフィルタで妨害波除去を行う.場合によっては、このフィルタは受信側波形整形用ナイキストフィルタ (通常、Root Raised Cosine フィルタ: RRC) の機能を兼ねる.変調方式が周波数変調 (FSK) あるいは差動位相変調 (DPSK) である Bluetooth では、システムの構成の容易さから、受信信号とその遅延信号を用いた非同期検波を用いる場合が多い.受信信号とその遅延信号の複素共役の積をとると、

$$(a(t)\exp(j\theta(t))) \times (a(t-\Delta t)(\exp(j\theta(t-\Delta t)))^* = a(t)a(t-\Delta t) \cdot \exp(j(\theta(t)-\theta(t-\Delta t)))$$

となり、 $\Delta t$  を 1 シンボル間の遅延とするとシンボル間の位相変化情報が得られる(遅延検波). また、振幅成分 a(t) が一定である GFSK 方式の場合、遅延量  $\Delta t$  が小さければ、上式の虚部(Q 成分)は、振幅を無視して

$$\sin(\theta(t) - \theta(t - \Delta t)) \approx \theta(t) - \theta(t - \Delta t) \approx \frac{d\theta(t)}{dt} \Delta t = \omega(t) \Delta t$$

となり近似的に周波数情報が得られる (FSK 復調).

また、遅延信号との差分をとる前に I/Q 信号から CORDIC などのアルゴリズムを用いて、位相を算出したのち、その遅延信号との差分をとることでデータを復調することも可能である (このときは  $2\pi$  rad から 0 rad への位相のジャンプが時々発生するのでその処理が必要である). Bluetoothの EDR ではパケット内で GFSK から $\pi/4$ -QDPSK、8DPSK に切り替わるため、復調器の動作も切り替える必要があるが、いずれも似通った構成となるため、ブロックを共有し簡素化することも可能である.遅延信号を用いた検波方式では、送受信機間の周波数オフセットは一定の位相オフセットとなり補正が容易である.

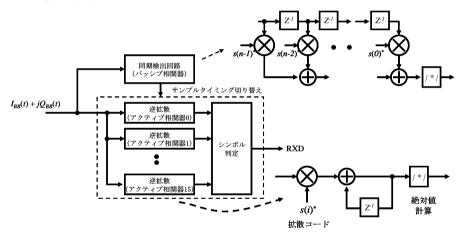

ZigBee においてもディジタル復調器の周波数変換,フィルタリングの部分は同様であるが,直接拡散方式を用いているため,逆拡散の処理が必要となる.受信パケットの先頭に存在する既定のプリアンブルとその拡散コードとの相関ピークを検出して,シンボル及びチップの判定タイミングの同期を図る.チップの判定タイミング検出のため,この相関器はチップレートよりも高速に動かす必要がある.チップの判定タイミングが検出後,チップレートと同じクロックで受信データをサンプリングし,各シンボルの拡散コードとの相関を検出して,データ判定を行う.

**図4・10** ZigBee 復調器の相関器の構成例(O-QPSK の場合)

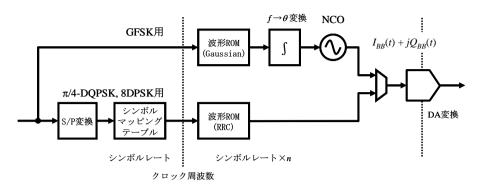

### 4-2-4 変調器におけるディジタル信号処理

送信側では、パルス整形フィルタのインパルス応答を ROM に蓄えて、送信ベースバンドデータに応じて読み出して送信波形を構築した後、DA 変換してアップコンバージョンを行う方式が、汎用性の点から採用されるケースが多い. 波形 ROM (テーブル)のインパルス 応答は、通常その長さは数シンボル分にわたり、波形を構築するには各シンボルに対する応答を加算する必要がある.

**図 4·11** の構成例のように、Bluetooth においては、GFSK 用の Gaussian 波形テーブルから データを読み出し波形を構成する。積分器で周波数データを位相データに変換して、NCO で 入力位相に対応する cos/sin の値を出力する。π/4-DOPSK、8 DPSK では、ベースバンドデー

タを対応する I/Q シンボルにマッピングし,各シンボルに対応するナイキストフィルタ (RRC) のインパルス応答波形を読み出して波形を構築する.

図4・11 Bluetooth の変調器構成例

ZigBee でもほぼ同様の構成で変調器が実現できる. ただし,直接拡散を行うので、シンボルとして拡散コードが与えられる. 例えば、2.4 GHz 帯の ZigBee では 4 ビットのベースバンドデータに対して、16 通りの 32 ビット拡散コードの中から対応するコードを割り当て、O-OPSK 変調を行う.

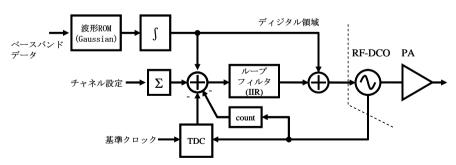

一方、定包絡線変調である GFSK や正弦半波波形を用いた O-QPSK では、PLL 2 点変調方式も用いられる。また、最近では **24・12** のように All-Digital PLL (AD-PLL) を用いて RF 発振器の位相をディジタルで制御して変調をかけ、その出力を高効率増幅器で増幅する送信機アーキテクチャも報告されている 3 これらの方式は、アップコンバージョンミキサが不要であり、非線形高効率アンプが使用できることから、低電力化、低コスト化へつながる技術として期待が高い。

図 4・12 All-Digital PLL を用いた定包絡線変調器の例 3)

### 4-2-5 まとめ

近年,ポータブル機器の普及ともに小電力無線規格が注目を集めている. 低コスト,低電力を目指すために必然的にシンプルな変調方式が採用され、当初アナログ回路で構成されて

いた変復調器も最近はディジタル信号処理による変復調が主流となっている.変復調器の信号処理そのものは既存技術でほぼ実現できる.ただし、要求性能が比較的緩いということもあり、AD-PLL を用いた変調器のように新しいアーキテクチャなどが最初に試される面白い分野でもある.また今後、環境発電で動作するようなセンサネットワークへの応用を考えると、さらなる消費電力の削減が要求され、そのために新たなアーキテクチャ、信号処理技術が考案されることが期待される.

# ■参考文献

- J. C. Haartsen, S. Mattisson, "Bluetooth-a new low-power radio interface providing short-range connectivity," Proceedings of the IEEE, vol.88, no.10, pp.1651-1661, Oct. 2000.

- E. Callaway, et al., "Home networking with IEEE 802.15.4: a developing standard for low-rate wireless personal area networks," IEEE Communications Magazine, vol.40, no 8, pp.70-77, Aug. 2002.

- 3) R. B. Staszewski, "All-digital TX frequency synthesizer and discrete-time receiver for Bluetooth radio in 130-nm CMOS," IEEE Journal of Solid-State Circuits, vol.39, no.12, pp.2278-2291, Dec. 2004.

# 4-3 DTV/DVD

(執筆者:甲斐直行) [2009年12月受領]

ディジタルテレビ(DTV)放送では、映像、音声のディジタルデータが圧縮符号化/多重化、伝送路符号化され、変調伝送される。ディジタルテレビ受信機は、この逆の手順で、元の映像、音声データを取り出すことが基本機能となる。LSI の集積度の向上により、これらの基本機能の大部分に加え、映像、音声の表示制御、システム全体の制御用の CPU を 1 チップに集積されるようになった。本節では、DTV 用 SoC(Syetem on Chip)の構成、及び各モジュールがどのように制御されるかについて述べる。また、DVD(Digital Versatile Disc)及びBD(Blu-ray Disc)について DTV との相違点を簡単に説明する。

### 4-3-1 ディジタル TV 用 SoC の基本的な構成

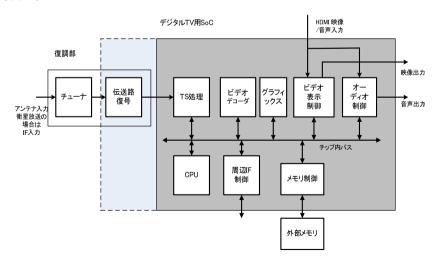

ディジタル TV 用 SoC の基本的な構成を**図 4・13** に示す <sup>3)-5)</sup>. ディジタル TV の復調部からの Transport Stream(TS)信号を処理する TS 処理部,映像ストリームをデコードするビデオデコーダ,デコード結果をディスプレイ機器に出力するためのビデオ表示制御部,グラフィックス表示データ生成のためのグラフィックス部,音声ストリームをデコードし音声信号を出力するオーディオ処理部,全体の制御を行う CPU,周辺 IO を制御する周辺 IO 制御部,DRAMで構成される外部メモリを制御するメモリ制御部,などからなる.CPU は,OS として Linuxを用いることが多く,SMP 構成をとることもある.また,外部機器からの映像音声を表示するための,HDMI などによるビデオ,音声入力機能をもつことが多い.放送の変調方式に応じて,復調と誤り訂正を行い TS を出力する伝送路復号部も取り込んだディジタル TV 用 SoCも出てきている.

**図4・13** ディジタル TV 用 SoC の構成

### 4-3-2 TS 処理と AV 同期機構

ほとんどの放送方式で、映像、音声の多重化に MPEG-2 システム標準の TS を用いている <sup>2)</sup>. TS 処理部で TS に対し必要に応じてスクランブル解除を行い、映像、音声のストリームを抽出する. 抽出されたストリームは、ES (Elementary Stream) または PES (Packetized Elementary Stream) として、外部メモリ中のストリーム用リングバッファに格納される.

TV 受信機では、TS 制御部が抽出した TS の到達時刻を表すタイムスタンプ PCR (Program Clock Reference)を用いて、VCXO などを用いて基準となる 27 MHz クロックである STC (System Timer Clock)を作成する。映像、音声のデコード/表示に用いられるサンプルクロックを、この 27 MHz から PLL を用いて生成して関連付けることで、デコード/表示の速度を放送に合わせることができる。MPEG-2 システム標準では、TS 入力と各デコーダのストリーム消費をモデル化した仮想デコーダ STD (System Target Decoder)を定義している。放送局側では、STD に対しストリームバッファのオーバーフロー、アンダーフローを生じさせないように TS のエンコードし、TS 中に表示/デコード用タイムスタンプ PTS/DTS (Presentation Time Stamp/Decoding Time Stamp)を与える。TV 受信機側では、映像、音声デコード処理遅延、表示処理の遅延差などの STD モデルとの差異を考慮に入れて、デコード開始の制御を行うことで、バッファ管理と AV 同期をとることができる。

# 4-3-3 ビデオ及びオーディオデコード

限られた放送帯域で伝送するために、映像、音声情報は、高圧縮率で圧縮符号化されている. 表 4・5 に示すように、放送で用いられる映像圧縮方式は、MPEG-2 と MPEG4-AVC/H.264 (以下 H.264) のいずれかである. H.264 は MPEG-2 に比べて高い圧縮率が実現できる、処理量及び DRAM のバンド幅消費量が大きくなる. インターネットを経由した IP 放送に対応するために VC-1 のデコード機能を内蔵したり、またインターネット上の動画再生のために、MPEG-4 ASP などのデコード機能をもつこともある.

| 女子 シールエフノアル及び自由スフリコノンジェ、江州ガス |            |                    |               |         |         |

|------------------------------|------------|--------------------|---------------|---------|---------|

|                              | 地上デジタル放送方式 |                    |               | 蓄積メディア  |         |

|                              | ISDB-T     | DVB-T              | ATSC          | DVD     | BD      |

| 放送地域                         | 日本,ブラジル    | 欧州など               | 北米,韓国         |         |         |

| 多重化方式                        | MEPG-2 TS  | MPEG-2 TS          | MPEG-2 TS     | MPEG-2  | MPEG-2  |

|                              |            |                    |               | PS      | TS      |

| 映像圧縮方式                       | MPEG-2     | MPEG-2             | MPEG-2        | MPEG-2  | H.264   |

|                              | H.264      | H.264              |               |         | MPEG-2  |

|                              |            |                    |               |         | VC-1    |

| 音声圧縮方式                       | MPEG-2 AAC | MPEG2-BC           | Dolby Digital | Dolby   | Dolby   |

|                              | MPEG-2 BC  | Dolby Digital      |               | Digital | Digital |

|                              |            | Dolby Digital plus |               | PCM     | PCM     |

|                              |            | HE-AAC             |               |         | DTS     |

表 4・5 地上デジタル放送と蓄積メディアの多重、圧縮方式

### 4-3-4 ビデオ表示制御

ビデオデコーダによるデコード結果の画像をディスプレイ機器に出力するまでに以下の処理が必要である。

#### (1) RGB 変換

映像の圧縮符号化では、色の表現に輝度 Y, 色差 Cb, Cr を用いており、表示機器に送る際に RGB に変換する必要がある. 変換マトリックスは、SDTV の場合は ITU-R601 に、HDTV の場合は ITU-R709 に従う.

# (2) プログレッシブ変換

インターレース方式の動画をプログレッシブ表示の表示機器に表示するためにプログレッシブ変換が必須である.これにより、例えば毎秒 60 枚のフィールドデータから毎秒 60 枚のフレームデータを作成する.

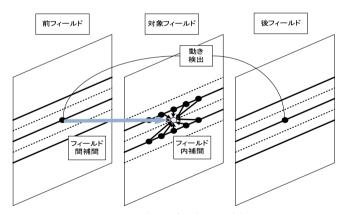

一般的に用いられる方式は、動き適応型プログレッシブ変換と呼ばれる(**図 4·14**). インターレース動画は、例えフレームピクチャとしてとして符号化されていても、二つのフィールドは異なる時刻のデータであるので、2フィールド合わせてフレームとして表示することはできない. 一方、フィールド内で垂直補間を行うと、静止画での垂直解像度の低下が目立つ. そこで、画素ごとに動きを検出し、動き部分に対してはフィール内での補間で画素を生成し、静画部分には隣接フィールドのデータを用いる. この方式では動き部分の垂直解像度が低下するため、動きベクトルを検出して動き部分に対しても隣接フィールドから画像を作成する、動きベクトル補償型プログレッシブ変換が用いられることもある<sup>9</sup>.

**図4・14** 動き適応型プログレッシブ変換

#### (3) フレームレート変換

液晶ディスプレイを用いた TV セットで、動きの不自然さを解消するために、プログレッシブ変換結果の秒 60 枚にから 120 枚にフレームレートを倍にすることが一般的になってきている。この場合、フレーム間で動きベクトルを検出し、それを用いてフレームデータを補間して新しいフレームを生成することが必要になる。

#### (4) 解像度変換

映像ソースと表示機器の解像度が異なる場合、スケーリング変換が必要である。一般的

には水平,垂直用の FIR フィルタによってスケーリングを実施する.特に画像を拡大する場合で,画像の特徴を抽出した結果に基づき,あるいは別時刻のフレームの画像を併せてスケーリングを行う手段を超解像度と呼ぶことがあり、各種の方式が提案されている<sup>7)</sup>.

### (5) ノイズ除去

画像のフレーム間の高い相関を利用してノイズを除去することができる. ノイズ除去は プログレッシブ変換前のデータに対して行う.

## (6) グラッフィックス表示機能

動画の映像デコード画像に同期してグラフィックスのデータを DRAM 中のグラフィックスフレームバッファから読み出し、ビデオデータと重ね合わせて表示データを生成する. グラフィックスデータには、データ放送のように放送の一部として送られて提示の仕方も規定があるものと、ユーザインタフェース仕様として受像機側で付加するものがある.

# 4-3-5 外部メモリ制御

ディジタル TV 用 SoC は、ビデオデコード処理と表示処理で大量のバンド幅を消費する.また多くの外部メモリをアクセスするモジュールをもつという特徴がある。民生機器はコスト要求が厳しく、外部メモリとして用いる DRAM の容量、ビット幅をあまり大きく取ることはできない。メモリ制御部は、次の3点の条件を満たすように、DRAM アクセスの順序を入れ替えて DRAM アクセスを最適化する。

- (a) DRAM アクセス効率の最大化

- (b) 各要求元に対するバンド幅保証

- (c) CPU などの低レイテンシーが必要な要求元に対するレイテンシーの最小化

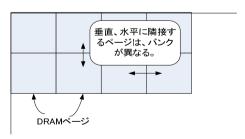

H.264 や MPEG-2 のデコード処理では、動き補償のための参照画像読み出しで、DRAM のページとバンクに対して**図 4・15** のような mapping を取ることが多い. これにより、参照画像読み出しがなるべく同一ページ内からの読み出しになり、同一ページに収まらない場合でも別バンクからのリードになり、DRAM アクセスのオーバヘッドが避けられる.

### フレームバッファ

図 4・15 フレームバッファの DRAM へのマッピング

# 4-3-6 DVD

DVD 及びBD のプレーヤで用いられる多重化方式, 映像・音声圧縮方式を表 4·5 に示した. DVD プレーヤでは, DVD の復調・復号化後の処理は, 多重化が MPEG-2 PS (Program Stream)

であることを除くと、DTV 用 SoC とほぼ同様の機能である. 使用する映像圧縮方式は、VC-1が加わっている.

DVD及びBDレコーダでは、エンコード機能が必要である. デジタル放送を録画する場合、送られてきた TS に対して、DVD であれば CPRM (Copy Protection for Recordable Media), BD であれば AACS (Advanced Access Content System) に従って暗号化して記録する. 映像がMPEG2 で圧縮符号化されている場合は、H.264 にトランスコードすることでデータ量を削減できる. トランスコードの方式としては、MPEG-2 のデコード結果を再エンコードするものと、エンコードの際に MPEG-2 の情報を用いる方法の両方がある.

#### ■参考文献

- 1) 日本放送協会編, "NHK デジタルテレビ技術教科書,"

- ISO/IEC 13818-1 Information technology—Generic coding of moving pictures and associated audio information: Systems

- 3) 礒邉三男,鎌田剛弘, 落合利之, 寒川賢太, 松井尚巳, 仲居祐二, 清家 守, "デジタルテレビ用システム LSI 及び PDP ドライバ," Matsushita Tech. Journal, 52, no.1, pp.74-82, 2006.

- 4) 田坂尚康, 中谷 隆, 音田敏宏, "デジタルテレビ用第3世代 SoC," 東芝レビュー, vol.63, no.7, pp.8-11, 2008

- T. Takizawa and M. Hirasawa, "An efficient memory arbitration algorithm for a single chip MPEG2 AV decoder," IEEE Transactions on Consumer Electronics, vol.47, no.3, pp.660-665, 2001.

- 6) 山内日美生, "進化する高画質化デジタル要素技術," 東芝レビュー, vol.63, no.6, pp.15-18, 2008.

- 7) "美に挑む規格外テレビ," 日経エレクトロニクス, 2009.2.9, pp.37-56, 2009.

# 4-4 ゲーム

(執筆者:永松正人) [2009年4月 受領]

## 4-4-1 家庭用ゲーム機の変遷

家庭用ゲーム機は、計算機の処理能力を最大限に消費する計算機応用のひとつである.これまでゲームとしては、よりきれいな動画をリアルタイムに生成することを求めてきており、そのための要求計算処理能力には今のところ限りが見えない.ゲームから要求される計算性能と、現状の最高性能の計算機の性能とを比べてみると、まだまだ前者の方が高くその期待に十分に応えるものを提供できているとはいえない.

これまでのゲーム機の開発では、ゲームの要求性能を満たす(近づける)ために、新しい 高性能な専用プロセッサを開発してきた。ゲームが計算機の演算処理能力向上の面での進歩 をリードしており、ゲーム機の進歩と計算機の進歩とは表裏一体のものであった。

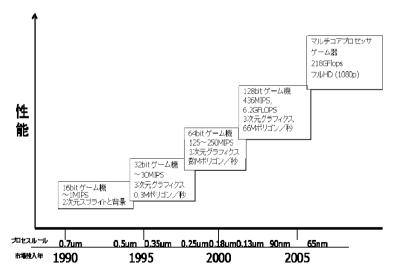

**図 4・16** に 1990 年代からの代表的な家庭用ゲーム機とその性能・機能の向上を示している。 家庭用ゲームとして目指してきたのは仮想現実の実現であり、よりリアルでかつきれいな動 画作りであるといえる.

このために

- 1:物理事象を忠実に再現する計算処理能力向上

- 2:グラフィック処理能力向上

の2点が開発にあたっての重要な要素となってくる. 常に最先端の計算機技術が導入され、 世代を追うごとにほぼ1桁以上の性能強化が求められ、実現されてきたことがわかる.

図4・16 主な家庭用ゲーム機の性能の向上

# 4-4-2 ゲーム機の構成例

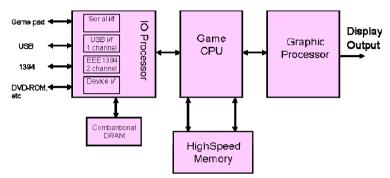

図 4・17 にゲーム機の代表的な構成例を示す。ゲーム機には、

1:物理シミュレーションを行う CPU (Central Processing Unit)

2:結果を表現する Graphic プロセッサ

3: インタフェース IO プロセッサ

の三つの機能(プロセッサ)から構成され、各々が独立したチップで構成される場合が多い.

図4・17 代表的なゲーム機の構成図

CPUには物理現象のシミュレーションのための高速・高精度のプロセッサ処理能力が要求される。このために処理能力重視の並列アーキテクチャが指向されることとなり、RISC プロセッサ、スーパースカラプロセッサ、マルチコアプロセッサなどの、最先端のマイクロプロセッサ技術が導入されている。浮動小数点演算が重要視され、専用の浮動小数点演算器を並列に複数個併設した構成となっている。データ処理能力の向上にともない高いデータ供給能力を提供する必要があり、低レイテンシー・高バンド幅のメインメモリシステムが必要となる。

Graphic プロセッサは高並列,高データ量の演算処理が主体となり,ここでも高バンド幅のメモリが必要となる。また,汎用プロセッサからグラフィックプロセッサへのデータ転送能力も重要であり,この間をいかに高バンド幅の専用バスで接続するかが重要となる。特に汎用プロセッサとグラフィックプロセッサとが別チップで構成される場合には,高速 IO インタフェースが重要となる。

IO プロセッサはコマンド入力の処理やデータロード,保存,他システムとのインタフェースを司ることとなり,ゲームの多様化,ネットワーク化にともない重要度が増してきている.

# (1) Cell/B. E. ™ プロセッサの構成<sup>1)</sup>

ゲーム向けの CPU の具体例として、セルプロセッサの構成を紹介する.

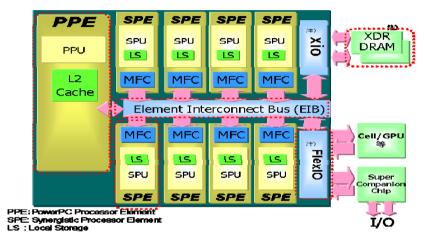

Cell Broadband Engine <sup>™</sup>プロセッサ (以下 Cell/B.E. <sup>™</sup>プロセッサ) は PowerPC アーキテクチャ互換である PPE 汎用プロセッサとデータ処理に最適化された 8 つの専用プロセッサ SPE (Synergistic Processor Element) をもつ非対称型のマルチコアの構成となっている. 汎用プロセッサである PPE が制御系処理を行い、SPE がデータ処理を受け持つという役割分担がなさ

れている. リソースコントロールや汎用のプログラム実行は PPE で行われ, データ処理に特化した専用プログラムは SPE で処理されることになる. 実施のゲームでのデータ処理は主に SPE が担当し、SPE の制御及び SPE 間のフロー制御は PPE が担当することになる.

9つのコアはチップ内の EIB (Element Interconnect Bus) という 4 系統の 128 ビットリング バスで結合されており、96 B/cycle (Peak) のバンド幅を有している. メモリインタフェース としては最大 25.6 GB/s 高バンド幅をもつ 2 チャネルの XDR 向けインタフェースをサポート しており、他チップとのインタフェースには最大 76.8 GB/s のバンド幅をもつ FlexIO を採用している. FlexIO はセルチップとのマルチチップ接続や、Graphic プロセッサとの接続、IO プロセッサとの接続に用いられる。セルチップの構成図を図 4・18 に示す。

図4・18 Cell/B.E.<sup>™</sup> プロセッサ構成図

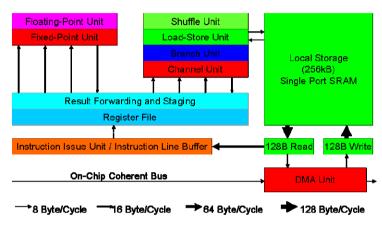

Cell/B.E.™ プロセッサ¹の演算能力性能を支えているのは、8 つ搭載されてSPEである. SPE はデータ処理に特化したシンプルな構成をしている. 最大 2 命令同時に発行・実行できるスーパースカラの方式を採用しており、整数演算と浮動小数点演算との独立したパイプラインを備えている. SIMD (Single Insatruction/Multiple Data) 方式を採用しており、最大 4 つの単精度浮動小数点データを同時に処理できる. Out Of Order処理のような複雑な制御系の導入を避ける一方、汎用レジスタを 128 本まで増強しソフトウェアパイプラインによる高速化処理を可能にしている.

**図 4·19** に SPE の内部構成図をしている. メモリアーキテクチャも複雑な制御を要するキャッシュの採用を避けて、256 KB の命令・データ兼用の専用 LS(Local Storage)をもち、LS 上にロードされた命令、データに対して処理を行うアーキテクチャとなっている. PPE・メインメモリを含む「外界」とのインタフェースには MFC(Memory Flow Controller)と呼ばれる DMA コントローラを介して行われる. MFC 内に MMU をもちアドレス変換処理を行っ

<sup>&</sup>lt;sup>1</sup> Cell Broadband Engine<sup>™</sup>プロセッサは株式会社ソニー・コンピューターエンタテイメントの商標.

ている. アドレス変換処理を SPU のデータ処理と分離しているために, 高効率のデータ処理 が実現できている.

命令のフロー制御に関しては命令ラインバッファ(16 命令×6 段)をもち、通常フローの命令の先読みのほかに、ソフトウェアによる分岐予測(Hint 命令による分岐先命令の先読み)をサポートしている.

SPE は制御系の処理オーバヘッドを最小限に抑えることにより、高い演算処理能力を達成している。

図4・19 SPE 構成図

# 4-4-3 今後の動向

これまでは、据え置き型のゲーム機を高性能の計算機という位置付けで説明してきた.据え置き型のゲーム機でもゲーム環境の制限から性能と消費電力のトレードオフが存在しており、事実、消費電力制限がゲーム機の処理性能を制限してきた.一方、ゲーム機の動向としては、据え置き型から携帯型のへの比重が高まってくるものと予想される.携帯型のゲーム機の機能的な要件はこれまで説明してきた(据え置き型の)家庭ゲーム機と変わるものではないが、電池寿命の制限から消費電流制限がより厳しくなり、これまで以上に処理性能と消費電力とのトレードオフが厳しく問われることとなる.電池駆動の制限の中でいかに性能を引き出すかということが重要になってくる.これまでのピーク性能、ピークバンド幅重視の指向から、バランスのとれた総合的なアーキテクチャ構成が重要となってくる.

また、ゲーム自体もこれまでのきれいでリアルな「絵」創りの視点に加えて、ゲームとしての「面白さ、楽しさ」を求める視点が加わり、幅広いインタフェース機能を備えたものがより重要となってくる。これまでのコマンドパッドによるコマンド入力に加えて、重力、加速度センサによる入力、音声認識、画像認識による入力など多岐にわたる入力手段の重要度が増してくる。IOプロセッサの機能・性能の拡張がより重要になってくるものと予想される。

それでもゲームは最先端の処理技術を求めるアプリケーション分野であることには間違いなく、今までと同様、計算機処理技術と同調して進歩していくことに間違いはない.

# ■参考文献

林 宏雄, "Cell Broadband Engine Processor 概要~ その設計思想と応用例," 電子情報通信学会集積回 路研究会招待講演, 2006 年 1 月 26 日 -1 月 27 日

# 4-5 ロボット

(執筆者:石川正俊・小室 孝・山崎信行) [2009年10月受領]

### 4-5-1 全体システム

最初にロボット制御における情報処理の流れについて解説する. 典型的なセンサを用いた アクチュエータのフィードバック制御は、以下のような流れで情報処理が行われる.

- 1. 制御対象となるべき事象の観測値(位置、速度、電流など)をセンサによって獲得

- 2. センサ情報を元に目標値などと比較して制御アルゴリズムに従い次の制御値などを計算(具体的な処理は各種制御アルゴリズムに依存)

- 3. その計算値を元にアクチュエータの制御

上記の流れを一定周期ごとに繰り返して行うことにより、ひとつのアクチュエータの制御を行う.アクチュエータが複数ある場合には、上記の流れを独立して並列に行う必要がある. 複数のアクチュエータを同時に制御して複雑な動作を行うようなロボットなどでは、各々の制御に依存関係があり、互いのセンサ情報を参照しながら、全体の情報処理を行う必要がある.

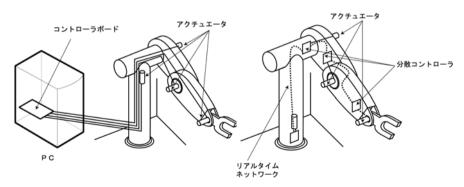

# (1) 集中制御

制御における情報処理の方式として最も古くから行われているのは集中制御という方式である.集中制御とは、一つのコンピュータ(パーソナルコンピュータ、組込みマイコンなど)ですべての I/O(センサ、アクチュエータなど)を集中的に制御する方式である.例えば、ロボットアームをパーソナルコンピュータで集中制御することを考える.典型的には、パーソナルコンピュータに必要な制御ボード(A/D コンバータボード、D/A コンバータボード、PWM 発生器ボードなど)を挿し、それら制御ボードを用いてロボット全体の制御を行う(図4・20(a) 参照).

(a) 集中制御

(b) 分散制御

図4・20 ロボットアームの集中制御と分散制御

### (2) 分散制御

現在のシステムでは、ひとつのプロセッサがすべてを制御するということは稀であり、多かれ少なかれ複数のプロセッサによって分散制御を行っている。例えば、ロボットアームを分散コントローラを用いて分散制御することを考える。典型的には、I/O 制御機能とネットワーク機能が付いた分散コントローラを用いてロボット全体の制御を行う(図 4・21(b) 参照).分散制御の場合、ほとんどの場合、組込み用プロセッサが用いられている。組込み用プロセッサの多くは計算機資源(計算能力、メモリなど)に制約があるため、完全な分散制御ではなく、プランニングなどの重い処理は PC で行い、制御のみを分散型で行うハイブリッドな制御形態のロボットも存在する。

組込み用プロセッサとしては、組込みマイコンが使用される場合も多いが、積和演算に強い DSP (Digital Signal Processor) が使用される場合も多い、どのようなプロセッサが使用されるかは、そのロボットの制御アーキテクチャに強く依存する。例えば、アクチュエータ(モータ)制御のためだけの演算(典型的には PID 制御の計算)を行う場合は計算量が少なくて済むので、演算能力の低い組込みマイコンで十分である。逆に、逆運動学を解こうとする場合、処理の重い行列演算を行う必要があり、演算能力の高い PC 用の汎用プロセッサや高速な DSP を用いる必要がある。

### 4-5-2 ネットワーク

# (1) センサネットワーク

複数のセンサを接続するためのネットワークをセンサネットワークと呼ぶ. 国内においては、インテリジェントルーム/ビルなどにセンサを張り巡らせる場合であるとか、ユビキタスコンピューティングなどに用いられる用途の際に、センサネットワークという用語が用いられる場合が多い. また、ロボット制御のためのセンサ及びアクチュエータが接続されたネットワークもセンサネットワークと呼ばれる場合がある. ロボットの場合、体内 LAN と呼ばれることもある. これらの用途の場合、ネットワークには、一定以上の安定性が望まれ、更にはリアルタイム性が望まれる場合も多い.

それに対して、米国などでは、自然環境や構造物などに多くのセンサを取り付けて(自然環境の場合にはばらまくというイメージに近い)モニタリングを行う際に、センサからの情報を集めるためのネットワークをセンサネットワークと呼ぶ場合が多い。これらの用途の場合、ネットワーク媒体には無線通信が望まれる場合も多く、ネットワークにはロバスト性が望まれる場合が多い。

## (2) リアルタイムネットワーク

分散制御を行う際には、ほとんどの場合に分散ノード間の通信にリアルタイム性が要求される. リアルタイム通信には、大きく

- ソフトリアルタイム通信

- ハードリアルタイム通信

の2種類が存在する. ソフトリアルタイム通信は、多少のデッドラインミスを許容するリアルタイム通信であり、通信のバンド幅保証によって実現する場合が多い. バンド幅を保証し、そのバンド幅内でマルチメディアデータ(映像、音声)などを流すことを目的としている.

それに対して、分散制御を実現するためには、通信データが相手に届くまでの時間を保証するハードリアルタイム通信がほとんどの場合に必要となる.

動画像などのマルチメディアデータのリアルタイム転送においては、データが多少壊れたとしても影響はほとんどない。例えば、画像の一部分が化けていたり、音声データの一部が化けていても、ほとんどユーザにはわからない。しかしながら、制御の場合には通信されたデータに誤りがあると、制御が不可能になるかもしれないし、事故などにつながるかもしれない。手軽に利用可能なリアルタイム通信(IEEE 1394 のアイソクロナス転送など)には、エラー訂正を行わないものが多いので注意が必要である。

分散制御用のネットワークを選択する際には、それ以外にもネットワークトポロジー、 Plug & Play 機構、消費電力などに注意する必要がある.

### (3) ロボット向けネットワーク規格

現在, ロボット制御に使用可能な通信インタフェースとしては Ethernet, IEEE-1394, USB 2.0, CAN, Responsive Link などの様々な規格が存在している.

### (a) Ethernet

Ethernet は、現在最もポピュラな汎用ネットワーク用の通信インタフェースであり、容易に利用できるというというのが最大の利点である。現在、100 Mbps の規格(100 Base-TX)と 1 Gbps の規格(1000 Base-T)が主に使用されている。CSMA/CD 方式を採用しており、通信の際に衝突があった場合は再送するというプロトコルである。したがって、通信の際に全く衝突がなければ通信レイテンシーが小さく通信速度も速いが、一度衝突が生じると再送を行い始めるので最悪通信時間を規定できずリアルタイム性がないという大きな問題点がある。関連して、ベストケースとワーストケースの差が非常に大きいというのが問題となる。制御用途に使用する場合、Ethernet の特性をよく理解したうえで用いる必要がある。

# (b) IEEE1394

IEEE1394 は、主に AV 機器やパーソナルコンピュータの I/O 機器を接続するための規格であり、アイソクロナス転送によってソフトリアルタイム通信を実現することができる。400 Mbps の規格 (IEEE 1394a) が PC には利用されているが、現在では 800 Mbps の規格 (IEEE 1394b) も使用され始めている。しかしながら、アイソクロナス通信モードではエラー訂正を行っていない、最大通信ノード数が 63 と少ない、Plug & Play 時にネットワーク全体にリセットがかかる、トポロジーがスター構造のみでループを許さない、耐故障性がないなど、制御用リアルタイム通信としては問題点も存在する。したがって、IEEE 1394 の特性をよく理解したうえで用いる必要がある。

### (c) USB

USB は、Universal Serial Bus の略称である。主にパーソナルコンピュータの I/O 機器を接続するための規格であり、豊富な PC 用 I/O 機器を手軽に接続することが可能である。11 Mbps の規格 (USB 1.1) と 480 Mbps の規格 (USB 2.0) があり、現在では USB 2.0 が主流となっている。最大通信ノード数が 127 と少ない、トポロジーがツリー構造のみでループを許さない、必ずルートコントローラ (PC) が必要である、耐故障性がないなど、制御用リアルタイム通信としては IEEE 1394 と同様に問題点もある。したがって、USB の特性をよく理解したうえで用いる必要がある。

#### (d) CAN

CAN は Controller Area Network の略称である。CAN の最大転送レートは 1 Mbps と低速であるが、元々は車載用 LAN として開発された規格であるので、制御系 LAN としての機能を有している。エラー検出機能を有しており、マルチマスター方式をとり、バスアクセスにも優先順位が付与される。バスの優先順位は ID の小さいものの優先度が高くなる。通信の最小単位であるメッセージのサイズが 0 byte~8 byte と非常に小さくしているため、スループットは悪くなるが、再送信などの場合には再送までの時間が短くなる。

## (e) Responsive Link

Responsive Link は分散リアルタイムシステム用に設計されたリアルタイム通信規格であり、多くのユニークな特徴を有している <sup>4)</sup>. リアルタイム処理の理論はプリエンプションを前提にして構築されているが、通信においてプリエンプションを実現する媒体は存在しなかった. Responsive Link は通信におけるプリエンプションを初めて実現し、リアルタイム処理の理論を通信に応用可能にしている. 具体的には、パケットに優先度を付加しノードごとに高優先度パケットが低優先度パケットの追い越しを行うことによるプリエンプティブな通信を実現している.

それ以外にも、ハードリアルタイム通信(イベントリンク)とソフトリアルタイム通信(データリンク)を分離して独立に通信、リンクの種類ごとに別経路を設定することが可能、パケットの優先度が異なると優先度ごとに別経路を設定することが可能で専用回線や迂回路を容易に実現可能、ノードごとに優先度を付け替えることが可能であり分散管理型でパケットの加減速を制御可能、256 レベルの優先度、ハードウェアによる前方エラー訂正(FEC)、通信速度を動的に変更可能、などの機能によって柔軟なリアルタイム通信を実現している 50. 現在のレスポンシブリンクの一方向の最大通信速度は800 Mbaud であり、通信速度は消費電力を抑えるために動作中に動的に変更可能である。Responsive Link は、現在、国内においては情報処理学会試行標準 ITSJ 0006:2003 として標準化されている 50. 国際的には、ISO/IEC JTC1 SC25 におい標準化され、ISO/IEC 24740:2008 として国際標準化されている.

### 4-5-3 ロボット用プロセッサ

### (1) ロボット用コントローラ

ロボット用コントローラは、既存の組込みマイコンと ADC, DAC, PWM 発生器、パルスカウンタなどの I/O チップを組み合わせて、独自の制御ボードを設計することが多く、ロボット制御に特化したコントローラチップは多くは存在しない。ロボット向けとして画像処理や音声処理用のプロセッサやボードはいくつか存在している。

ロボット用分散コントローラモジュールとしては、東工大で開発された TITech Wire と呼ばれるシリアルバス通信に接続される分散コントローラ群がある  $^{11}$ ). 東大では、 $I^2$ C によって接続される小型のモータモジュールやセンサモジュール群を開発している  $^{12}$ ). ロボット用制御プロセッサとしては、小型ヒューマノイド用に用いられている(株)電産の Sage CPU Module がある.

また、NEDO 次世代ロボット共通基盤開発プロジェクト (2005~2007 年度) において、産業技術総合研究所による SH-4 ベースの運動制御モジュール、富士通による ASIC を用いた画像処理モジュール、NEC による FPGA と組み合わせた音声処理モジュールの開発が行われた.

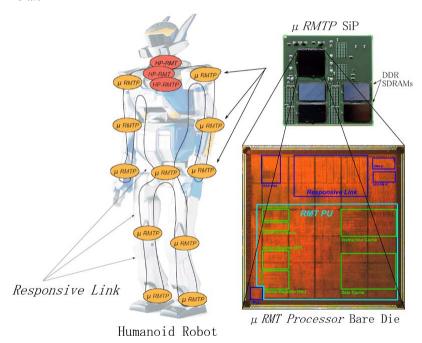

#### (2) RMT Processor

RMT Processor は、分散リアルタイムシステム(特にロボットの分散制御)を実現するために、リアルタイム通信・処理・制御を同時にハードウェアレベルで行うことを目的にして設計を行ったシステム LSI である。先に開発した Responsive Processor ではハードウェアによるリアルタイム通信機構(Responsive Link)のみ有し、リアルタイム処理機構は有していなかったが、RMT Processor では、ハードリアルタイム通信・処理及びソフトリアルタイム通信・処理の両方を行うことができるように設計されている。

分散制御用のプラットホームとして様々なシステムの中に容易に組み込んで使用できるようにするために、RMT Processor はロボット制御に必要な機能であるリアルタイム処理機能 (RMT PU), リアルタイム通信機能 (Responsive Link), コンピュータ用周辺機能 (DDR SDRAM I/Fs, PCI-X, USB 2.0, IEEE 1394, Ethernet, DMAC など), 各種周辺制御機能 (PWM Generators, Pulse Counters など) のすべてを 1 チップに集積 (System-on-a-chip) している (**図 4・21** 参照).

図4・21 RMT Processor を用いたヒューマノイドロボットの分散制御

システム設計者は RMT Processor に必要な I/O (センサ, アクチュエータ, ディジタルカメラなど) を接続するだけで必要な機能を実現できる. それら I/O を接続し固有の機能を有した RMT Processor をそのシステムにふさわしいトポロジーで Responsive Link を用いて複数個接続することによって, 分散リアルタイムシステムを構築する. チップ単体で使用した場合でも, 例えば IEEE 1394 に接続されたディジタルカメラでキャプチャした動画像を内蔵ベク

トルユニットでリアルタイム処理しながら、同時にその処理結果を基にパルスカウンタと PWM 発生器を制御してアクチュエータの制御を行い、システム全体のリアルタイム制御を 行う(ビジュアルフィードバック制御)というようなことが可能である.

RMT Processor のプロセッシングユニットである RMT PU のリアルタイム処理アーキテクチャ (RMT Architecture) は、ハードウェアで様々なレベルのリアルタイム処理をサポートしている。RMT Architecture は、SMT <sup>6, 7</sup> と優先度を融合したリアルタイム処理向けマルチスレッドアーキテクチャである。具体的には、256 レベルの優先度付きのスレッドを優先度順に8スレッド同時実行(優先度付 SMT)することにより、コンテキストスイッチをすることなくリアルタイム実行を行う。更に、32 スレッド格納可能なコンテキストキャッシュ、優先度を用いたすべてのファンクショナルユニットの制御、割込み発生時のハードウェアによるスレッドの制御、共有レジスタを用いた複数スレッド間のデータ共有、同期ユニットを用いた複数スレッド間の同期、高性能2次元ベクトルプロセッサ、複数スレッドによるベクトルユニットの共有などの特徴的な機能によって、柔軟なリアルタイム処理を実現している <sup>9,10</sup>)。また、RMT PU のインストラクションセットは MIPS 上位互換となっている <sup>8</sup>).

### (3) 画像処理 LSI

ロボットが外界を知覚するセンサの中でも、人間の目に相当する視覚センサは多くの情報を取得できることから、ロボットを構成する重要な要素とされてきた。代表的な視覚センサは、撮像素子で画像を取り込み、それを情報処理することによってロボットの判断・行動に必要な状況認識を行っている。しかしながら、画像情報は一般にデータサイズが大きく、情報処理にかかる時間も長い。ロボットが状況の変化に素早く対応できるためには、少なくともビデオレートのリアルタイム処理が求められるが、ロボットに搭載可能な組込み CPU の演算能力では、その要求を満たすことは難しい。

1993 年に井上らは、SGS-Thomson 社の画像圧縮用 LSI である STI 3220E "Motion Estimation Processor (MEP)" を用いて、複数の注視領域におけるブロックマッチング処理を高速に行うビジョンシステムを開発した <sup>14)</sup>. 同システムは  $16 \times 16$  画素、20 領域をビデオレートで追跡することができるほか、オプティカルフロー計算やステレオ視にも利用できる.

1994年には金出らが PLD, ALU などの汎用部品と TI 社の DSP である TMS 320C40 を 8 つ 用いてビデオレートでステレオ視による距離画像を生成するシステムを構築した <sup>15)</sup>. 本システムは 6 台までのカメラを接続でき、マルチベースラインステレオ法により高精度、高信頼度の距離画像を出力することができる。200×200 画素、23 段階の視差探索範囲で毎秒 30 フレームの動作が可能である。

これらの市販部品を用いたシステムに対し、専用 LSI の開発も行われてきた。張山らは  $0.5 \mu m$  CMOS プロセスを用いて、 $512 \times 512$  画素のステレオマッチングを 60 ms で行う VLSI プロセッサを開発した  $^{16}$ . マッチング結果の信頼度をピクセルごとに測定し、それに基づいてウィンドウサイズを変更することで、高信頼度の距離画像を生成するようになっている.

中尾らは 2007 年に独立行政法人新エネルギー・産業技術総合開発機構 (NEDO) の「次世代ロボット共通基盤開発プロジェクト」において、次世代ロボットによる環境認識処理を高速化する画像認識用デバイスを開発した <sup>17)</sup>. 本デバイスは、ステレオビジョンに必要な相関演算、空間フィルタ演算、特徴抽出 (コーナー、線分) などの画像処理をシストリックアレ

イ演算回路を用いて並列に行うことで、高速処理を可能にしている. 2852 領域からのコーナー特徴の抽出とステレオマッチング(視差0~63 画素)を 27 ms で実行できる.

ロボット以外の組込み用途では、主に車載向けのビジョンプロセッサが多く作られている。例えば、 京らによる 128 個の 4 Way VLIW コアをワンチップに集積した高並列 SIMD プロセッサ IMAPCAR <sup>18)</sup> がその一例である。産業用ロボットの知能化や次世代ロボットの普及により、このような高性能画像プロセッサがロボットに搭載される可能性は高い。

# (4) ビジョンチップ

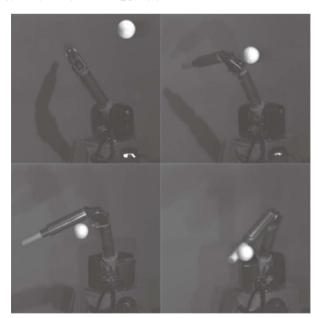

通常の視覚センサは,人間の目の特性に合わせて 30 fps 程度のフレームレートを目標に作られている.それに対し,より高いフレームレートを用いることで,人間を超える動体視力をもつロボットを実現するための視覚センサの研究が行われている.石川らは 1992 年に,光検出器と汎用の処理回路を 1 対 1 に対応させたビジョンシステムを開発した 199. 処理回路は 8 画素分を一つの CMOS ゲートアレイに実装しており,これを 512 個用いて作られた SPE-4kシステムは  $64\times64$  個の画素を有している.光検出器にはフォトトランジスタを用いており,全画素を並列に読み出している.また, $16\times16$  個の画素をもつ SPE-256 システムがアクティブビジョンに搭載され, 1 kHz のビジュアルフィードバックによる高速トラッキングを実現した 209. この成果は後に,センサ系・処理系・運動系の応答性能を操作対象の運動特性に合わせて設計すべきであるというダイナミクス整合という形で理論化され 219, その理論に基づいて様々なタスクを高速に行うロボットシステムが開発された. **図**  $4\cdot22$  は飛んでくるボールをアームで打ち返すロボット 229 の連続写真である.

図4・22 バッティングをするロボット

一方,高フレームレートのリアルタイムビジョンを実現するデバイスの開発も進められた. 前述のシステムは、光検出器と処理回路の間の配線が膨大になるという問題があったが、センサと処理回路をすべて半導体チップに実装することで、その問題は解決される. 小室らは、対象追跡に特化し、小型化を追求したビジョンチップ <sup>23)</sup> を開発した. **図 4・23** に評価ボードの写真を示す. 画素ごとにディジタル処理を行うビジョンチップは、画素面積が大きく画素数を増やすことが困難であったが、2008 年には、QVGA サイズ(320×240 画素)のビジョンチップ <sup>24)</sup> が開発されている.

**図4・23** 高速対象追跡ビジョンチップ

### ■参考文献

- 1) John A. Stankovic, "Misconceptions about real-time computing," IEEE Computer, pp.2-10, 1988.

- 2) Jane W. S. Liu, "Real-time systems," Prentice Hall, pp.159-179, 2000.

- 3) http://shark.sssup.it.

- 4) http://www.itscj.ipsj.or.jp/ipsj-ts/02 06/toc.htm.

- 5) 山崎信行,松井俊浩,"並列分散リアルタイム制御用レスポンシブプロセッサ,"日本ロボット学会誌,vol.19,no.3,pp. 68-77, April 2001.

- Susan J. Eggers, Joel S. Emer, Levy Henry M, Jack K. Lo, Rebecca L. Stamm, and Thilsen Dean M, "Simultaneous multithreading: A platform for next-generation processors," IEEE Micro, vol.17, no.5, pp.12-19, 1997.

- Dean M. Tullsen, Susan J. Eggers, Joel S. Emer, Levy Henry M, Jack K. Lo, and Rebecca L. Stamm, "Exploiting choice: Instruction fetch and issue on an implementable simultaneous multithreading processor," Proceedings of the 23rd Annual International Symposium on Computer Architecture, 1996.

- 8) http://www.ny.ics.keio.ac.jp/rmt/.

- 9) 薄井弘之, 内山真郷, 伊藤 務, 山崎信行, "Responsive Multithreaded Processor の命令供給機構," 情報 処理学会論文誌: コンピューティングシステム, vol.45 (SIG.11 (ACS 7)), pp.105-118, 2004.

- 10) 伊藤 務, 山崎信行, "分散リアルタイムネットワーク用プロセッサとその応用," 情報処理学会論文 誌: コンピューティングシステム, vol.44 (SIG 11 (ACS 3)), pp.226-235, Aug. 2003.

- 11) 広瀬茂男,中村 亨,福島 E.文彦,滝田謙介,"Titech Wire:ロボット制御用高速シリアル I/O の開発 インテリジェントコンタクト端子の設計,"ロボティクス・メカトロニクス講演会'01 講演論文集,

- 1A-A1, 2001.

- 12) Kei Okada, Akira Fuyuno, Takeshi Morishita, Takashi Ogura, Yasumoto Ohkubo, Yasuyuki Kino, Masayuki Inaba, and Hirochika Inoue, "Device distributed approach to expandable robot system using intelligent device with super-microprocessor," Journal of Robotics and Mechatronics, vol.16, no.2, pp.208-216, 2004.

- 13) "[特集]次世代ロボット共通基盤開発プロジェクトと RT コンポーネント," 日本ロボット学会誌, vol.27, no.2, pp.123-163, Mar. 2009.

- 14) 井上博允,稲葉雅幸,森 武俊,立川哲也,"局所相関演算に基づく実時間ビジョンシステムの開発," 日本ロボット学会誌,vol.13, no.1, pp.134-140, 1995.

- 15) 金出武雄, 蚊野 浩, 木村茂, 川村英二, 吉田収志, 織田和夫, "ビデオレートステレオマシンの開発," 日本ロボット学会誌, vol.15, no.2, pp.261-267, 1997.

- 16) M. Hariyama, T. Takeuchi, and M. Kameyama, "VLSI processor for reliable stereo matching based on adaptive window-size selection," Proceedings of 2001 IEEE International Conference on Robotics and Automation, pp.1168-1173, 2001.

- 17) 中尾 学, 沢崎直之, "画像認識用デバイスおよびモジュールの開発," 日本ロボット学会誌, vol.27, no.2, pp. 130-134, 2009.

- 18) 京 昭倫, "高並列アレイ型プロセッサ IMAPCAR のアーキテクチャとその技術展望,"電子情報通信 学会 集積回路研究会 (ICD) 技術研究報告, vol.107, pp. 97-102, 2007.

- 19) Masatoshi Ishikawa, Akira Morita, and Nobuo Takayanagi, "High Speed Vision System Using Massively Parallel Processing," Proceedings of 1992 IEEE/RSJ International Conference on Intelligent Robots and Systems, pp.373-377, 1992.

- 20) 中坊嘉宏,石井 抱,石川正俊,"超並列・超高速ビジョンを用いた1 ms ターゲットトラッキングシステム,"日本ロボット学会誌,vol.15, no.3, pp.417-421, 1997.

- Akio Namiki, Takashi Komuro, and Masatoshi Ishikawa, "High Speed Sensory-Motor Fusion Based on Dynamics Matching," Proceedings of the IEEE, vol.90, no.7, pp.1178-1187, 2002.

- 22) Taku Senoo, Akio Namiki, and Masatoshi Ishikawa, "High-Speed Batting Using a Multi-Jointed Manipulator," Proceedings of 2004 IEEE International Conference on Robotics and Automation, pp.1191-1196, 2004.

- 23) 小室 孝,石川正俊,石井 抱,吉田 淳,稲田喜昭,小宮泰宏,"高速対象追跡ビジョンチップの開発,"計測と制御,vol.43,pp.802-804, 2004.

- 24) Atsushi Iwashita, Takashi Komuro, and Masatoshi Ishikawa, "A 320x240 Pixel Smart Image Sensor for Object Identification and Pose Estimation," Proceedings of 2009 IEEE Symposium on Low-Power and High-Speed Chips, pp.331-346, 2009.

# 4-6 車載 LSI

(執筆者:馬路 徹·平尾眞也) [2008年12月受領]

## 4-6-1 車載 LSI 応用分野

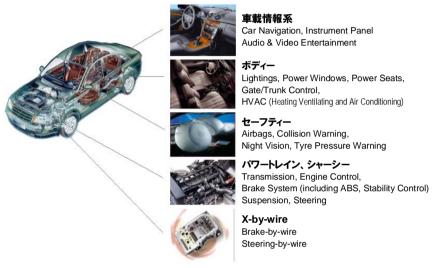

車載 LSI は車載情報系、ボディ、セーフティ、パワートレイン及びシャーシと大きく四つの分野に分かれている(**図 4・24**). これに機械的なワイヤーではなく、電気信号でアクチュエータを制御する X-by-wire 関連の LSI が加わる.

図4・24 車載 LSI 応用分野

車載情報系応用分野の中にはカーナビゲーション (ナビ), 計器パネル, オーディオ・ビデオ機器が含まれる. ここには GPS 信号処理, グラフィックス処理, ディジタルオーディオ, ディジタルビデオ処理のために多くの高性能 32 ビット RISC マイクロプロセッサ及び信号処理プロセッサが使用されている. 計器パネルでさえも機械式メーターに加えて, 各種情報をLCD で表示するために高度なグラフィックス処理能力が今後要求されてくる. 性能向上のペースは一番高く, 2010 年ごろよりマルチコアの導入が計画されている.

ボディ応用分野には、灯火装置、パワーウインドウ、パワーシート、トランク開閉、空調 関連機器制御用のマイクロプロセッサが多用されている。特別に高い信号処理性能は要求さ れておらず、8 ビット、16 ビットマイクロプロセッサが主に使用される。

セーフティ応用分野には広く普及しているエアーバッグのほかに、今後重要になってくる数々の安全技術が含まれている.前車との間隔をミリ波やステレオカメラなどで検知したり、障害物を画像認識で検知したりして衝突を警告もしくは回避するシステム、赤外線カメラからの入力から人間パターン認識し、前方画面にそのパターンを表示、警告するナイトビジョンがある。これらは高度の信号処理性能とともに高い信頼性が要求されている。

パワートレイン応用分野にはエンジン制御やトランスミッション制御があり、近年の厳しい排出ガス規制をクリアする目的で、年々要求されている処理能力が上がっている。デバイスとしては複雑なタイマなどの周辺を内蔵した32ビットRISCマイクロプロセッサが主に使用される。情報系と同様にこちらもマルチコア化の流れがある。ただしリアルタイム処理が非常に重要であり、SMPのようなOS任せのマルチプロセッサ制御技術は採用されない。

シャーシ応用分野にはブレーキ、ステアリング、サスペンション制御が含まれる。ブレーキに関しては ABS にはじまり、最近は自動車の姿勢を制御するスタビリティコントロールといった高度な制御技術も導入されている。複数 ECU の連携含め高度の信号処理が要求される。

最後に X-by-wire は電気信号でブレーキ, ステアリング制御を行うものであり, 高信頼性の重載ネットワーク, 制御技術が要求される.

本節では主に車載情報系のマイクロプロセッサ、信号処理プロセッサに関しての解説を行うが、パワートレイン系に関してもその性能動向に簡単に触れる.

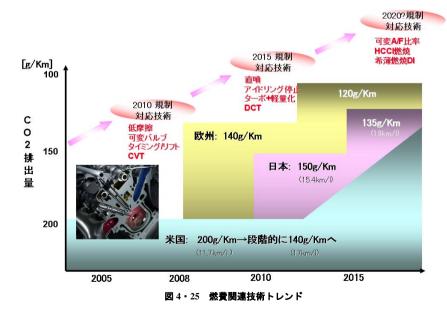

## 4-6-2 パワートレイン応用分野

環境保護, $CO_2$  排出量制限の世界的な動向からエンジン制御にはますます高度な信号処理技術が要求されてきている。**図 4・25** はガソリンエンジンに関する世界各国の法規制を示したものである。近年これら HC, NO<sub>x</sub>, PM などの規制に加え, $Co_2$  そのものの規制が各国で進んでおり,燃焼時の有害物質の制御のみならず,燃焼自体を大幅に改善することが急務となっている。

これに対応するために**図 4·26** に示すような様々なエンジン制御技術が開発されてきた. 1990 年代は薄い燃料混合比で排気ガスを抑えるリーンバーン制御, 1995 年代には燃料噴射,

エアフロー制御技術, 2000 年代には燃料直噴, 可変バルブ機構, 2005 年代にはモデルベース・ディジタル信号処理, 電磁バルブ, 高精度のエアフロー制御技術が導入されている. こうした制御の高度化に応じて, 1990 年代は 16 ビット CISC, 1995 年代は 32 ビット RISC, 2005 年代にはデュアルコアのマイクロプロセッサが製品化され, 動作周波数も継続的に向上している. オンチップフラッシュメモリ及び SRAM の容量も 1990 年代の 60kB/2kB から 2000 年代の 512kB/32kB, 2005 年代の 4MB/256kB と急速に増加している.

図4・26 エンジン制御技術及びマイクロプロセッサ仕様の動向

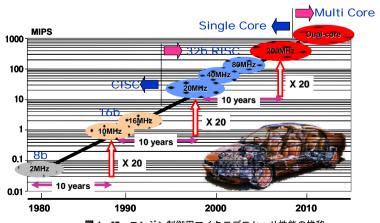

図4・27 エンジン制御用マイクロプロセッサ性能の推移

図4・27 は更に長期にわたって1980年代から2010年代に至るマイクロプロセッサのMIPS値をプロットしたものである. CISC からRISC に移行することにより飛躍的にMIPS値を向上させたが、このようにプロットしてみると興味深いことにコンスタントに10年間で20倍の性能向上を示している. このまま進めると2010年量産車以降は、リーク電流抑制の必要性から必然的にマルチコアが採用されることになる.

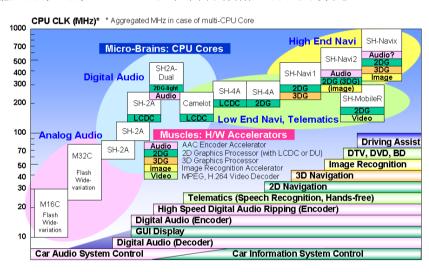

## 4-4-3 車載情報系分野

車載情報系はカーオーディオ用のシステムコントローラから運転支援,オーディオ・ビデオも含めた高度なナビシステムまで広範なアプリケーション,及び要求性能に及ぶ.性能範囲が非常に広範囲に及ぶために,これを対数メモリでプロットしたものが**図 4・28** である.性能指標はわかりやすくする意味で CLK 周波数 (MHz) を使用したが,同じ周波数でも実性能は CISC、RISC、スーパースカラ (2 命令同時実行) RISC により異なる.

図4・28 車載情報系マイクロプロセッサ要求性能

アナログオーディオ用のシステムコントローラは、CD/DVD プレーヤ、チューナの制御やマンマシンインタフェースの制御を司るマイクロプロセッサである。簡単な表示制御を行うこともある。要求される性能の上限は70 MHz 程度であり、16 ビット、32 ビットの CISC マイクロプロセッサで対応できる。処理性能は低いが、低消費電力、応答速度、多くの周辺機能の集積化など製品設計としては多くの課題を有する。

ディジタルオーディオ機器では MP3, AAC などのディジタル圧縮オーディオのデコード や, CD 上のオーディオデータを MP3, AAC エンコードする必要がある. デコードには 20  $\sim$ 30 MHz 程度, デコードには 50 $\sim$ 70 MHz 程度の処理性能が必要とされ, 浮動小数点や DSP 機能付きの 32 ビット RISC マイクロプロセッサが必要になってくる. このクラスのオーディオ機器になると, ディスプレイも QVGA クラスの LCD が使用されることもあり, CPU の描

画処理能力も要求さる. これらにより, この応用分野で要求されるのは 70 MHz 以上 400 MHz 程度の性能である. 最新のものにはやはりマルチコアが適用されている.

組込みローエンドナビは 2D グラフィックスをメインに,自動車の各種情報を表示する機能が要求される. その要求性能は 200~400 MHz 程度である. このあたりから,プロセッサのみの性能では処理能力が不足するので,例えば 2D グラフィックスに特化したハードウェアアクセラレータやプロセッサが使用される.

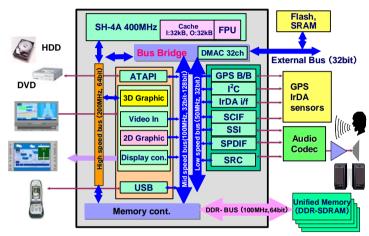

ハイエンドナビでは 3D グラフィックス,オーディオリッピング用の AAC エンコーダ,運転支援のために画像認識機能が導入されてくる. CPU の性能も 400~1000 MHz に向上するが,CPU では間に合わない信号処理のために 3D グラフィックスプロセッサ,AAC エンコーダ,画像認識プロセッサなどが使用される.

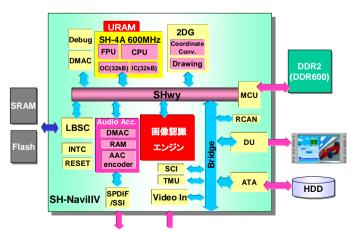

図4・29 第1世代のハイエンドナビ用プロセッサ

図4・30 第2世代のハイエンドナビ用プロセッサ

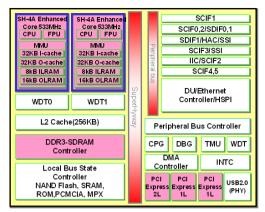

図4・31 第3世代のハイエンドナビに適用可能な汎用プロセッサ

図4・29 は第1世代のハイエンドナビ用プロセッサの例である. PC 用チップセットに例えれば、CPU プロセッサはもちろんのこと、外部 DDR メモリインタフェースやグラフィックスプロセッサを内蔵するノーズブリッジ、各種周辺を集積化したサウスブリッジをすべて集積化したシングルチップ PC に例えられるほどの高集積度である. これにより、2D/3D 地図描画、3D ランドマーク描画、経路探索、データベース検索、VICS 情報などを活用した渋滞回避処理などが実現できる.

**図 4·30** は第 2 世代のハイエンドナビ用プロセッサの例である。オーディオリッピング用の 12 倍速の AAC エンコーダプロセッサとともに、画像認識プロセッサが内蔵されている。 CPU 性能は第 1 世代の 400 MHz から 600 MHz にアップグレードされている。

図 4・31 は第 3 世代のハイエンドナビに適用可能な汎用プロセッサの例である. CPU コアはデュアルコアとなり、各々533 MHz の CLK 周波数である. ナビ用プロセッサのような各種周辺やグラフィックスプロセッサは内蔵されていないが、デュアルコアの性能を生かすために、PCI Express をはじめ Ethernet や USB 2.0 の高速インタフェースを内蔵している. PCI Express は 4 レーンを使用した場合、最大 800 MByte/sec 程度のデータ転送速度を実現する. PCI やこの例のような PCI Express などの高速外部バスにより、外部に任意のグラフィックスプロセッサ、DSP や FPGA を接続した柔軟なナビシステムを構築することが可能である.

# 4-4-4 CPU の処理負荷を低減する各種専用設計プロセッサ

3D グラフィックスには座標変換,ライティング効果の計算などに多次元の浮動小数点積和 処理を要する。また、描画に際してのテクスチャの貼り付け、深さ方向の処理など多くの データ転送を要する処理もある。これらを効率よく実行するには、汎用の CPU よりは専用に 設計されたプロセッサの方が実用的である。従来は固定機能を用いて 3D 描画を行っていたが、最新の 3D グラフィックスでは柔軟なシェーダ API を使用して高画質の描画を実現している。このためには、汎用のマルチスレッドエンジンが使用される。汎用エンジンであるために、H.264 や MPEG-4 ビデオストリームのデコードも可能である。

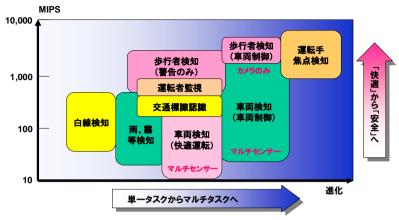

図4・32 画像認識に要求される処理性能

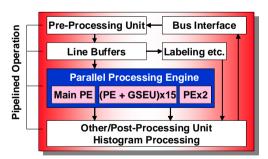

運転支援は今後高齢化社会も迎え、非常に重要な機能となってくる. その重要な技術要素に画像認識がある. **図 4・32** は画像認識に必要な CPU 性能を MIPS でプロットしたものである. 車線認識などは 500 MIPS 程度の性能のため CPU でも実現可能である. しかし、歩行者検知となると 5000 MIPS 程度の性能が要求され CPU や汎用 DSP での処理は厳しい. そこで画像認識に特化したプロセッサの導入が必要になってくる. **図 4・33** は第 2 世代ナビプロセッサに内蔵した画像認識プロセッサである. 高位レベルの判断及びデータ通信は汎用 CPUに任せ、画像認識の核となる繰り返し信号処理を実行する. 実行画像認識に特化した並列エンジンは正規化相関パターンマッチング実行に性能を発揮する. そして、容易なプログラミングのために 200 の API 関数が用意されている. このようなエンジンによりナビと連携して交通標識の認識、精度の高いレーン位置情報の認識が可能となる.

図4・33 第2世代ナビプロセッサに内蔵した画像認識プロセッサ

### ■参考文献

Toru Baji, "The Micro-Brains and Muscles for Automotive Electronics," 2007 ISSCC Visuals Supplement, SE4-3.